Cm_config register, Cm_config register -8 – Altera CPRI v6.0 MegaCore Function User Manual

Page 97

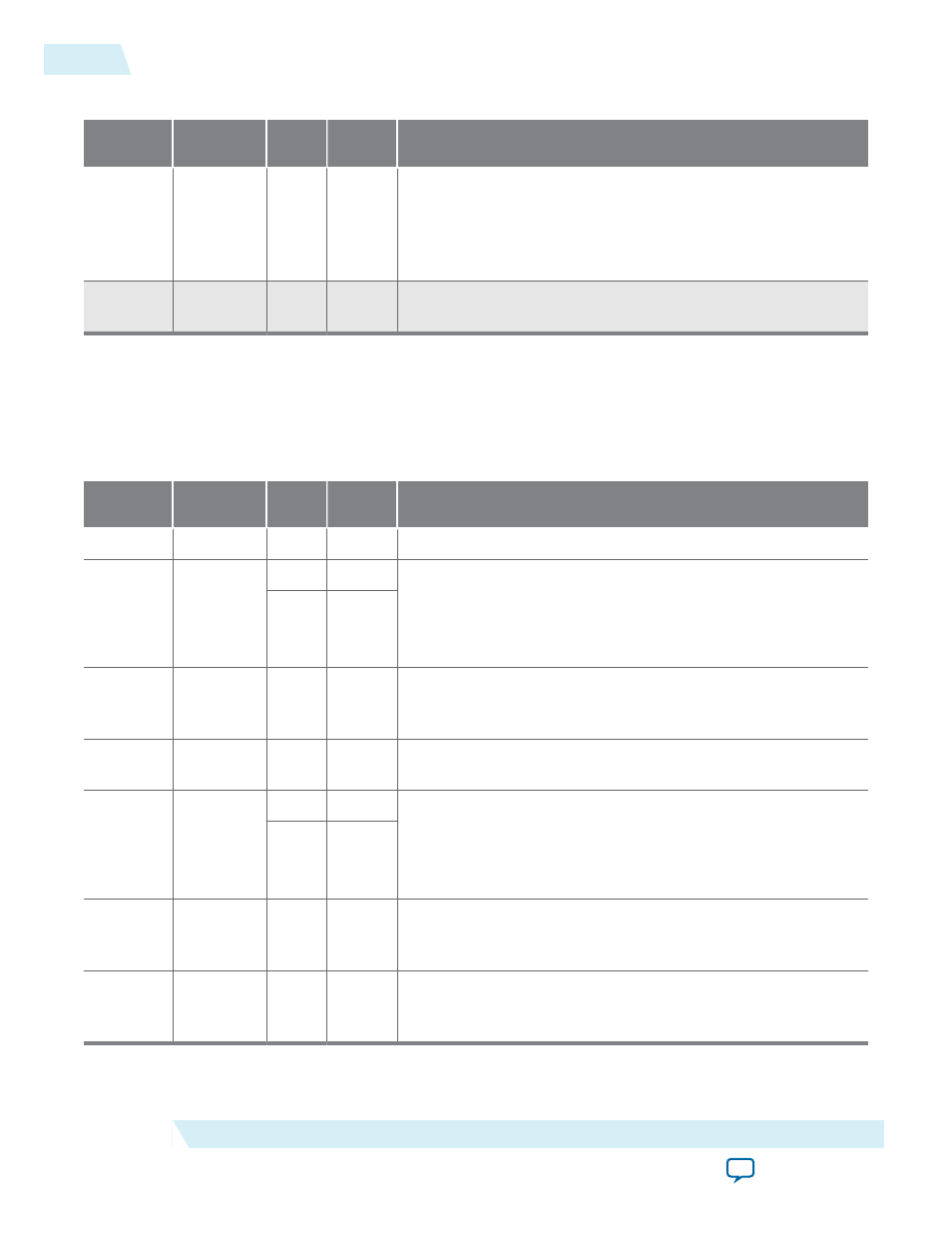

Table 5-9: CPRI v6.0 IP Core RX_SCR Register at Offset 0x18

Bits

Field Name

Type

Value on

Reset

Description

31

rx_scr_

active

RO

1'b0

Indicates that the incoming hyperframe is scrambled. The value

1 indicates that the incoming communication is scrambled, and

the value 0 indicates that it is not scrambled. The IP core

determines whether or not the incoming communication is

scrambled based on the protocol version.

30:0

rx_scr_

seed

RO

31'b0

Received scrambler seed. The receiver descrambles the

incoming CPRI communication based on this seed.

CM_CONFIG Register

Table 5-10: CPRI v6.0 IP Core CM_CONFIG Register at Offset 0x1C

Bits

Field Name

Type

Value on

Reset

Description

31:13

Reserved

UR0

19'b0

12

slow_cm_

rate_auto

RW

1'b1

Enable auto-negotiation of HDLC rate.

If you turn on Enable L1 inband protocol negotiator, this field

is a RW register field with the default value of 1. Otherwise, this

field is a RO register field with the default value of 0.

RO

1'b0

11

slow_cm_

rate_

filter

RW

1'b1

Enable filtering of HDLC rate.

10:8

tx_slow_

cm_rate

RW

3'b110

Rate configuration for slow Control and Management (HDLC).

To be inserted in CPRI control byte Z.66.0.

7

fast_cm_

ptr_auto

RW

1'b1

Enable auto-negotiation of Ethernet rate.

If you turn on Enable L1 inband protocol negotiator, this field

is a RW register field with the default value of 1. Otherwise, this

field is a RO register field with the default value of 0.

RO

1'b0

6

fast_cm_

ptr_

filter

RW

1'b1

Enable filtering of Ethernet rate.

5:0

tx_fast_

cm_ptr

RW

6'd20

Pointer to first CPRI control word used for fast Control and

Management (Ethernet). To be inserted in CPRI control byte Z.

194.0.

5-8

CM_CONFIG Register

UG-01156

2015.02.16

Altera Corporation

CPRI v6.0 IP Core Registers