Altera CPRI v6.0 MegaCore Function User Manual

Page 72

sections explain how you set and use these register values to derive the extended Tx delay measurement

information.

M/N Ratio Selection

As your selected M/N ratio approaches 1, the accuracy provided by the extended delay measurement

increases.

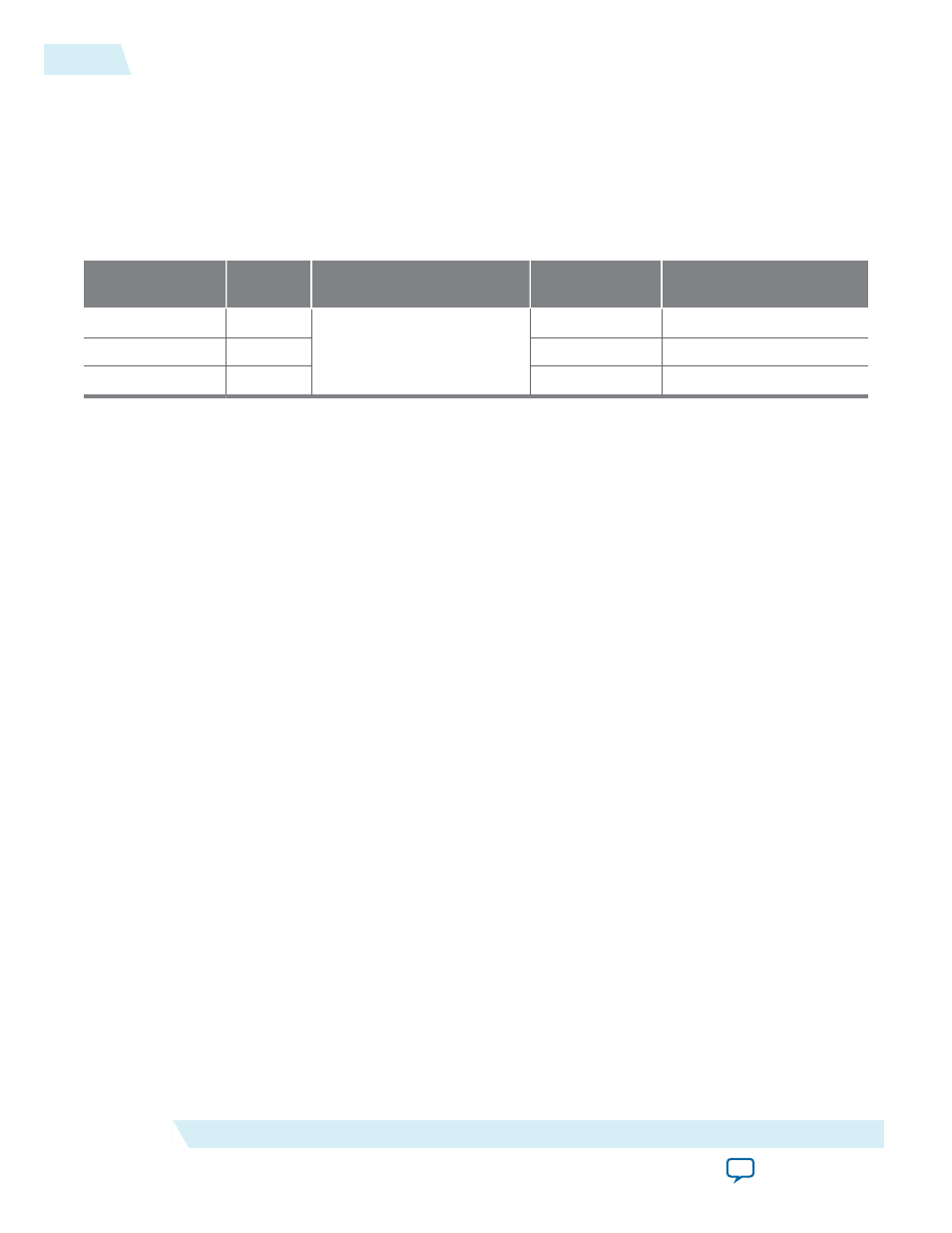

Table 3-15: Resolution as a Function of M/N Ratio at 3.072 Gbps

M

N

cpri_clkout Period

ex_delay_clk

Period

Resolution

128

127

13.02 ns (1/76.80 MHz)

13.12 ns

±100 ps

64

63

13.22 ns

±200 ps

1

4

3.25 ns

±3.25 ns

Example 3-3: Extended Delay Measurement Calculation Example

This section walks you through an example that shows you how to calculate the frequency at

which to run

ex_delay_clk

, and how to program and use the registers to determine the delay

through the CPRI Receive Buffer.

For example, assume your CPRI v6.0 IP core runs at CPRI line bit rate 3.072 Gbps. In this case,

the

cpri_clkout

frequency is 76.80, so a

cpri_clkout

cycle is 1/76.80 MHz.

If your accuracy resolution requirements are satisfied by an M/N ratio of 128/127, perform the

following steps:

1. Program the value N=127 in the

rx_msrm_period

field of the

RX_EX_DELAY

register at offset

0x54.

2. Perform the following calculation to determine the

ex_delay_clk

frequency that supports

your desired accuracy resolution:

ex_delay_clk

period = (M/N)

cpri_clkout

period = (128/127)(1/(76.80 MHz)= 13.123356

ns.

Based on this calculation, the frequency of

ex_delay_clk

is 1/(13.123356 ns)

The following steps assume that you run

ex_delay_clk

at this frequency.

3. Read the value of the

RX_EX_DELAY

register at offset 0x54.

If the

rx_ex_delay_valid

field of the register is set to 1, the value in the

rx_ex_delay

field

has been updated, and you can use it in the following calculations. For this example, assume

the value read from the

rx_ex_delay

field is 0x107D, which is decimal 4221.

4. Perform the following calculation to determine the delay through the Rx buffer:

Delay through Rx buffer = (rx_ex_delay x cpri_clkout period) / N = (4221 x 13.02083 ns) / 127

= 432.7632 ns.

This delay comprises (432.7632ns / 13 .02083 ns) = 33.236

cpri_clkout

clock cycles.

These numbers provide you the result for this particular example. For illustration, the preceding

calculation shows the result in nanoseconds. You can derive the result in

cpri_clkout

clock

cycles by dividing the preceding result by the

cpri_clkout

clock period. Alternatively, you can

3-42

Extended Delay Measurement

UG-01156

2014.08.18

Altera Corporation

Functional Description