Altera CPRI v6.0 MegaCore Function User Manual

Page 37

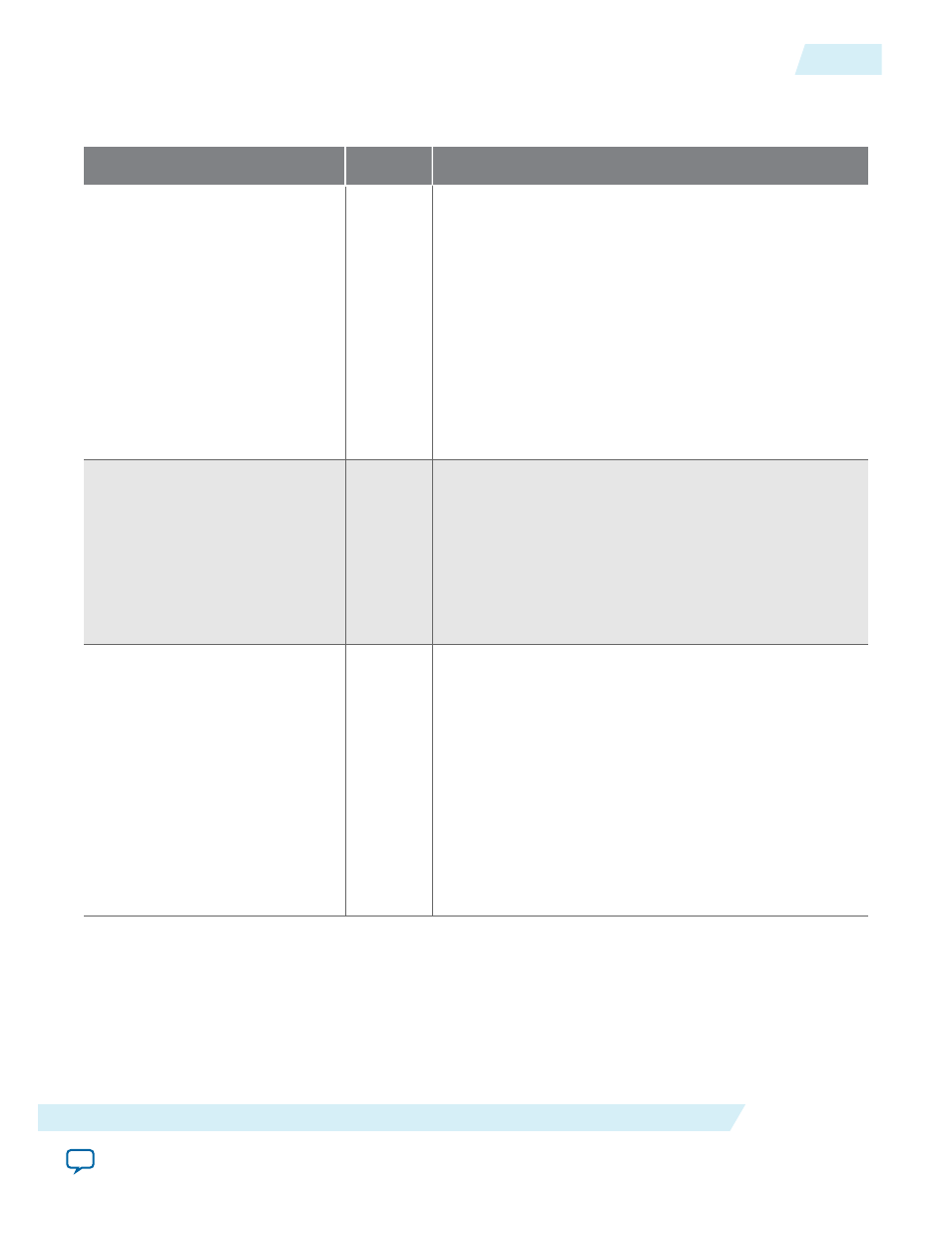

Table 3-4: Start-Up Sequence Interface Signals

All interface signals are clocked by the

cpri_clkout

clock.

Signal Name

Direction

Description

state_startup_seq[2:0]

Output

Indicates the state of the CPRI start-up sequence state

machine. This signal has the following valid values:

• 3'b000: State A: Standby

• 3'b001: State B: L1 Synchronization

• 3'b011: State C: Protocol Setup

• 3'b010: State D: Control and Management Setup

• 3'b110: State E: Interface and VSS Negotiation

• 3'b111: State F: Operation

• 3'b101: State G: Passive Link

This signal is available only if you turn on Enable start-up

sequence state machine in the CPRI v6.0 parameter

editor.

state_l1_synch[2:0]

Output

State B condition indicator. Indicates the state of the CPRI

receiver L1 synchronization state machine. This signal has

the following valid values:

• 3'b000: XACQ1

• 3'b001: XACQ2

• 3'b011: XSYNC1

• 3'b010: XSYNC2

• 3'b110: HFNSYNC

nego_bitrate_complete

Input

Indicates the CPRI line bit rate negotiation is complete.

Input from external CPRI line bit rate negotiation block.

If you do not turn on Enable auto-rate negotiation in the

CPRI v6.0 parameter editor, you should tie this signal

high.

This signal is available only if you turn on Enable start-up

sequence state machine in the CPRI v6.0 parameter

editor.

Asserting this signal advances the start-up sequence state

machine from state B to state C. The IP core writes the

value of this signal to the

nego_bitrate_complete

field of

the

START_UP_SEQ

register at offset 0x24.

UG-01156

2014.08.18

Start-Up Sequence Following Reset

3-7

Functional Description

Altera Corporation