Altera CPRI v6.0 MegaCore Function User Manual

Page 62

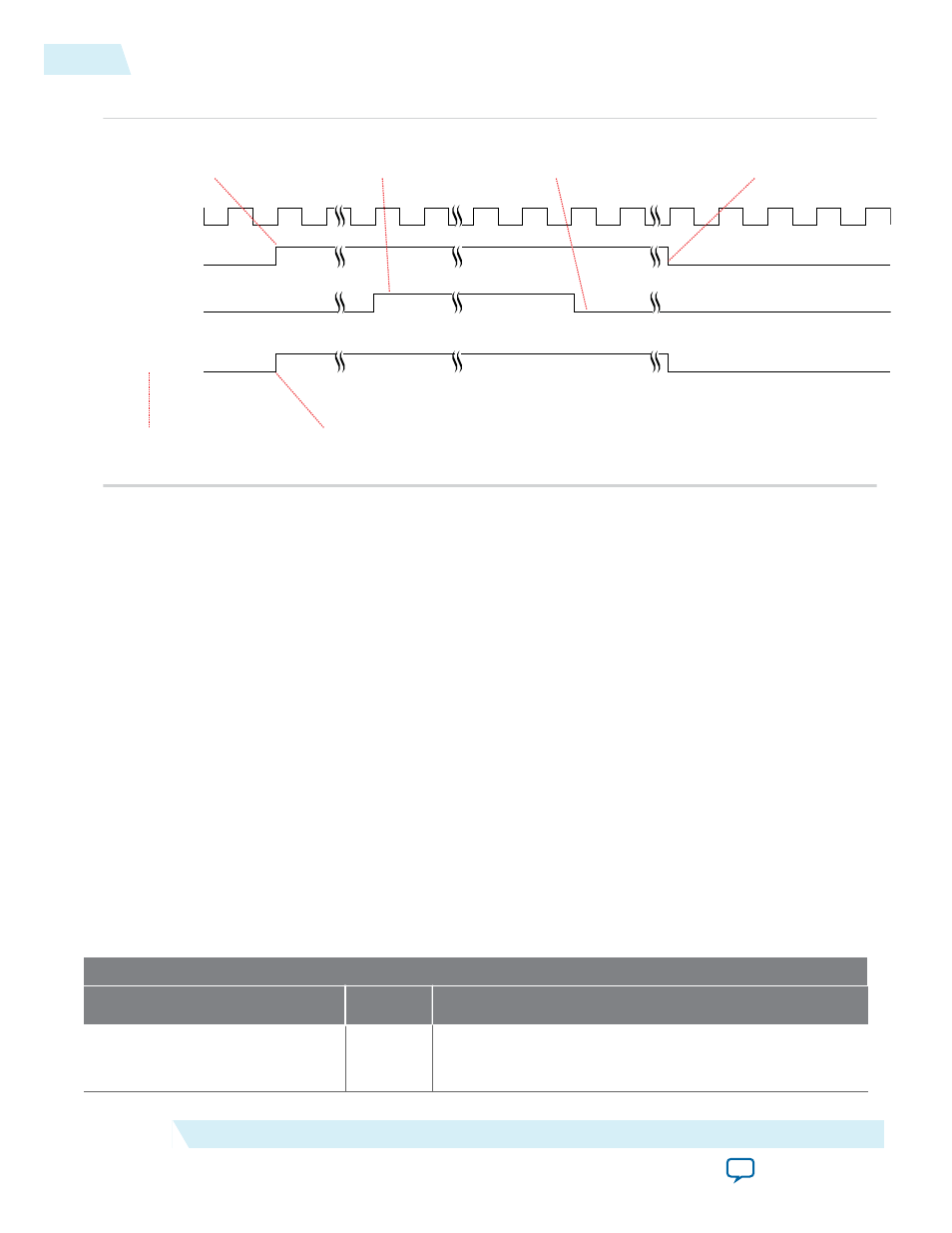

Figure 3-24: LOF, LOS, and RAI on Direct L1 Control and Status Interface

cpri_clkout

z130_local/remote_lof

z130_local/remote_los

z130_local/remote_rai

LOF Happens after RX

State Machine Lost

Comma Synchronization

May or May Not

Follow Up LOS

RX State Is Recovering

from Comma

Resynchronization

remote_lof/los/rai

Only Happens to Slave

RAI Asserts whenever

LOF or LOS Asserts

Hyperframe

Synchronization

Achieved

Related Information

on page 5-11

Media Independent Interface (MII) to External Ethernet Block

The media independent interface (MII) allows the CPRI v6.0 IP core to communicate directly with an

external Ethernet MAC block. If you turn on Enable IEEE 802.3 100BASE-X 100Mbps MII in the CPRI

v6.0 parameter editor, your IP core includes this interface.

The MII supports the bandwidth described in the CPRI v6.0 Specification in Table 12, Achievable

Ethernet bit rates, up to the CPRI line bit rate of 3.072 Gbps (maximum Ethernet bit rate of 105.6 Mbps).

Table 3-11: MII Signals

These signals are available if you turn on Enable IEEE 802.3 100BASE-X 100Mbps MII in the CPRI v6.0

parameter editor. You can connect a user-defined Ethernet MAC to this interface.

The interface is fully compliant to the IEEE 802.3 100BASE-X 100Mbps MII specification. An Ethernet PCS block

in the CPRI v6.0 IP core ensures the interface bandwidth matches the current CPRI line bit rate and accesses data

at the correct CPRI frame positions according to the Z.194.0 pointer value.

You must monitor the MII FIFO status signals and ensure you do not overflow or underflow the FIFO.

The interface signals are clocked by the

mii_rxclk

or

mii_txclk

clock.

RX MII Signals

Signal Name

Direction

Description

mii_rxclk

Input

Clocks the MII receiver interface. You must drive this

clock at the frequency of 25 MHz to achieve the 100 Mbps

bandwidth required for this interface.

3-32

Media Independent Interface (MII) to External Ethernet Block

UG-01156

2014.08.18

Altera Corporation

Functional Description