Extended delay measurement interface, Deterministic latency, Extended delay measurement interface -43 – Altera CPRI v6.0 MegaCore Function User Manual

Page 73: Deterministic latency -43

calculate the number of cpri_clkout clock cycles of delay through the Rx buffer directly, as

rx_msrm_period

/N.

Related Information

•

•

on page 5-18

•

Extended Delay Measurement Interface

Extended Delay Measurement Interface

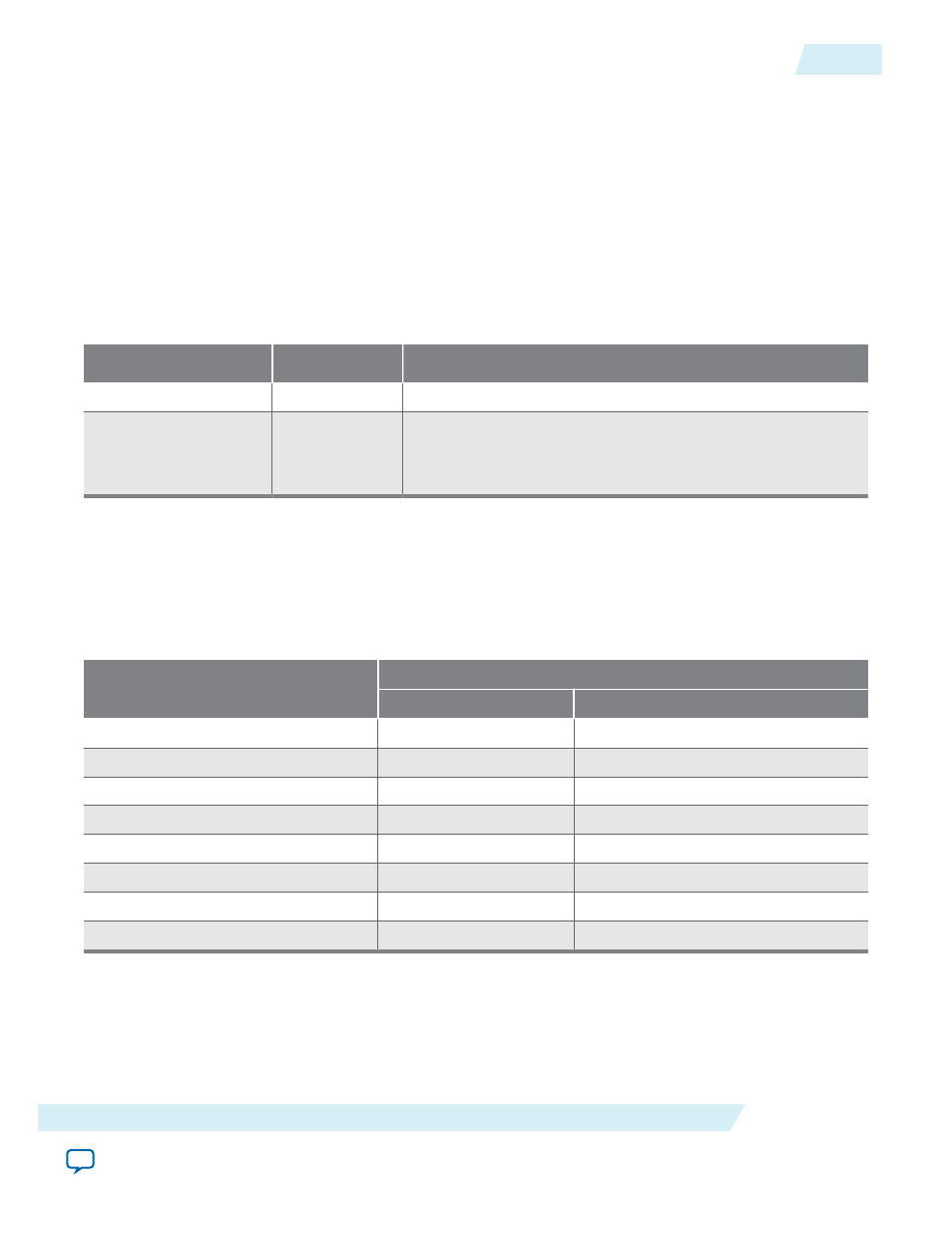

Table 3-16: Extended Delay Measurement Interface Signals

Signal Name

Direction

Description

ex_delay_clk

Input

Clock for extended delay measurement.

ex_delay_reset

Input

Resets the extended delay measurement block. This signal is

active low.

This reset signal is associated with the

ex_delay_clk

clock.

Deterministic Latency

The CPRI v6.0 IP core complies with CPRI V6.0 Specification requirements R-19, R-20, R-20A, R-21, and

R-21A.

Table 3-17: Frequency of Clocks for Delay Calculations

CPRI Line Bit Rate (Gbps)

Clock Frequency (MHz)

cpri_clkout

TX PCS and RX PCS clocks (internal)

0.6144

15.36

61.44

1.288

30.72

30.72

2.4576

61.44

61.44

3.072

76.8

76.8

4.9152

122.88

122.88

6.144

153.6

153.6

9.8304

245.76

245.76

10.1376

307.2

253.44

UG-01156

2014.08.18

Extended Delay Measurement Interface

3-43

Functional Description

Altera Corporation