Cpu interface to cpri v6.0 ip core registers, Cpu interface to cpri v6.0 ip core registers -35 – Altera CPRI v6.0 MegaCore Function User Manual

Page 65

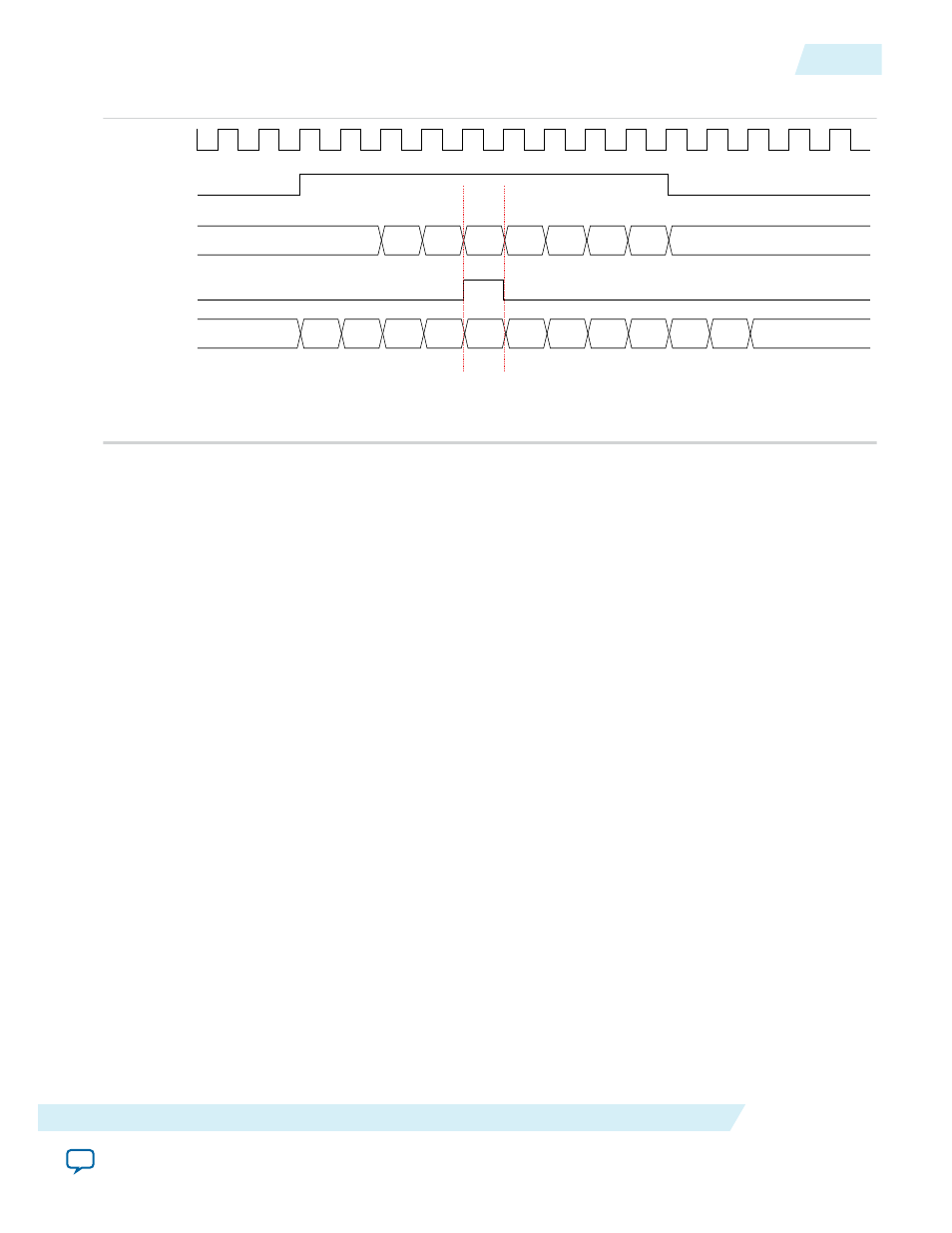

Figure 3-26: TX MII Timing Diagram

mii_txclk

mii_txen

mii_txd

mii_txer

Encoded Frame

D1

D2

D3

D4

D5

D6

D7

X

X

/J/

/K/

/D1/

/D2/

/F/

/D4/

/F/

X

/I/

/D6/

/D7/

/T/

/R/

Error Injection

Discard Part

of Payload

Related Information

CPRI v6.0 IP Core L2 Interface

CPU Interface to CPRI v6.0 IP Core Registers

Use the CPU interface to access the CPRI v6.0 IP core status and configuration registers. This interface

does not provide access to the hard transceiver configuration registers on the Arria 10 device.

If you turn on Enable all control word access in the CPRI v6.0 parameter editor, you can access all CPRI

hyperframe control words through this interface.

The control and status interface is an Avalon-MM slave interface. An on-chip processor such as the Nios

II processor, or an external processor, can access the CPRI v6.0 configuration address space using this

Avalon-MM interface.

Related Information

For more information about the Avalon-MM protocol, including timing diagrams, refer to the Avalon

Memory-Mapped Interfaces chapter.

UG-01156

2014.08.18

CPU Interface to CPRI v6.0 IP Core Registers

3-35

Functional Description

Altera Corporation