Altera CPRI v6.0 MegaCore Function User Manual

Page 52

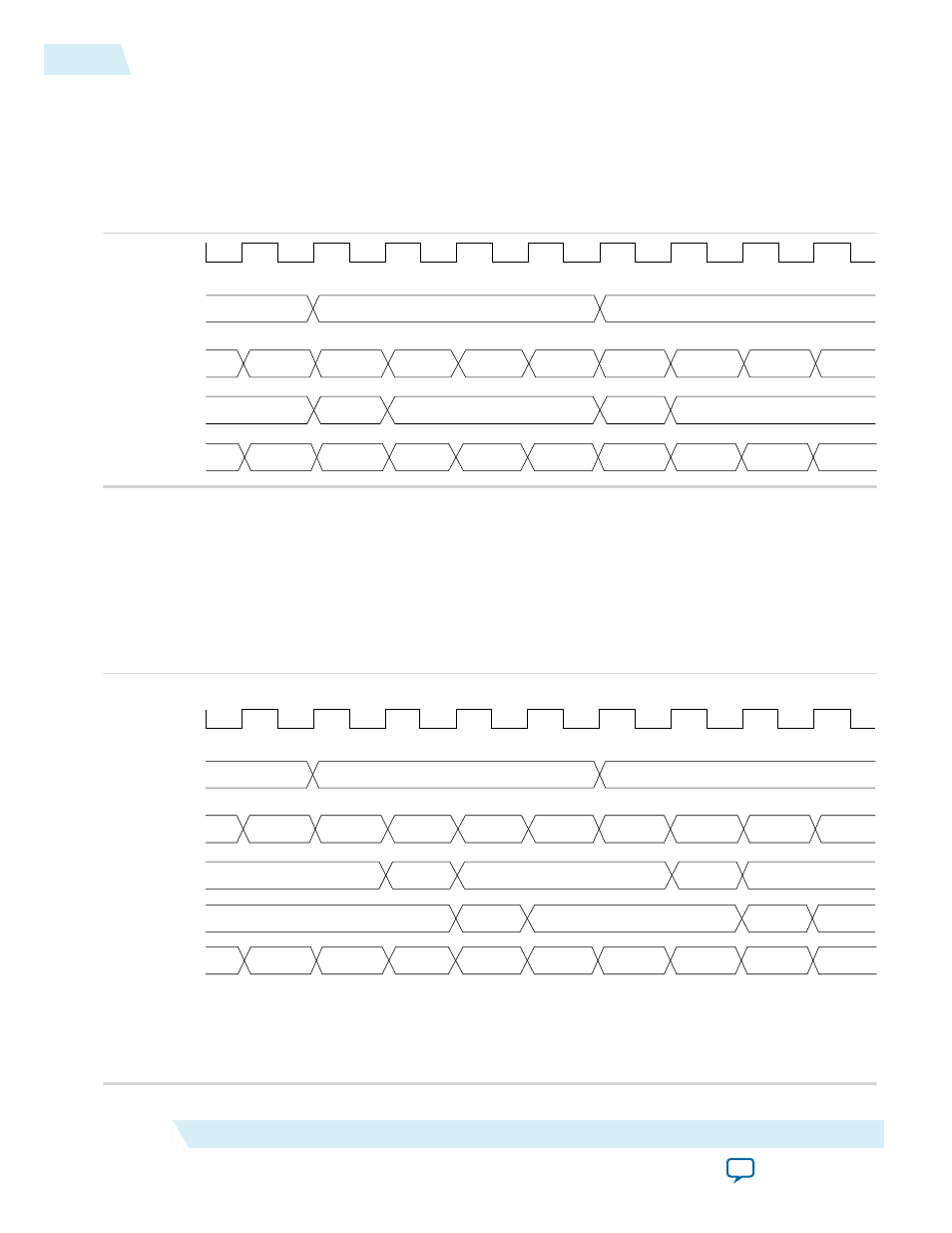

Figure 3-14: Direct IQ RX Interface Timing Diagram

Direct IQ RX interface behavior in a CPRI v6.0 IP core running at 0.6144 Gbps.

The

aux_rx_x

and

aux_rx_seq

signals are not part of this interface and are available only if you turn on

the AUX interface in your CPRI v6.0 IP core variation. However, their presence in the timing diagram

explains the timing of the

iq_rx_valid

output signal that you use to identify the clock cycles with valid

I/Q data.

cpri_clkout

aux_rx_x[7:0]

aux_rx_seq[6:0]

iq_rx_valid[3:0]

2

3

4

2

3

0

1

2

3

0

1

2

3

1111

0111

1111

0111

1111

(IQ)(IQ)

(IQ)(IQ)(IQ)(IQ)

X(IQ)(IQ)(IQ)

(IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ)

X(IQ)(IQ)(IQ)

(IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ)

iq_rx_data[31:0]

Figure 3-15: Direct IQ TX Interface Timing Diagram

Expected behavior on the direct IQ TX interface of a CPRI v6.0 IP core running at 0.6144 Gbps.

The

aux_tx_x

and

aux_tx_seq

signals are not part of this interface and are available only if you turn on

the AUX interface in your CPRI v6.0 IP core variation. However, their presence in the timing diagram

explains the timing of the

iq_tx_ready

output signal that you use to identify the clock cycles when you

can write I/Q data to the CPRI frame. Note that the write latency is two

cpri_clkout

clock cycles in this

example.

cpri_clkout

aux_tx_x[7:0]

aux_tx_seq[6:0]

iq_tx_ready[3:0]

iq_tx_valid[3:0]

2

3

4

2

3

0

1

2

3

0

1

2

3

1111

0111

1111

0111

1111

1111

0111

1111

0111

1111

(IQ)(IQ)

(IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ)

X(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ) (IQ)(IQ)(IQ)(IQ)

X(IQ)(IQ)(IQ)

(IQ)(IQ)(IQ)(IQ)

iq_tx_data[31:0]

Auxiliary latency cycle(s) == 1

3-22

Direct IQ Interface

UG-01156

2014.08.18

Altera Corporation

Functional Description