Extended delay measurement, Extended delay measurement -41 – Altera CPRI v6.0 MegaCore Function User Manual

Page 71

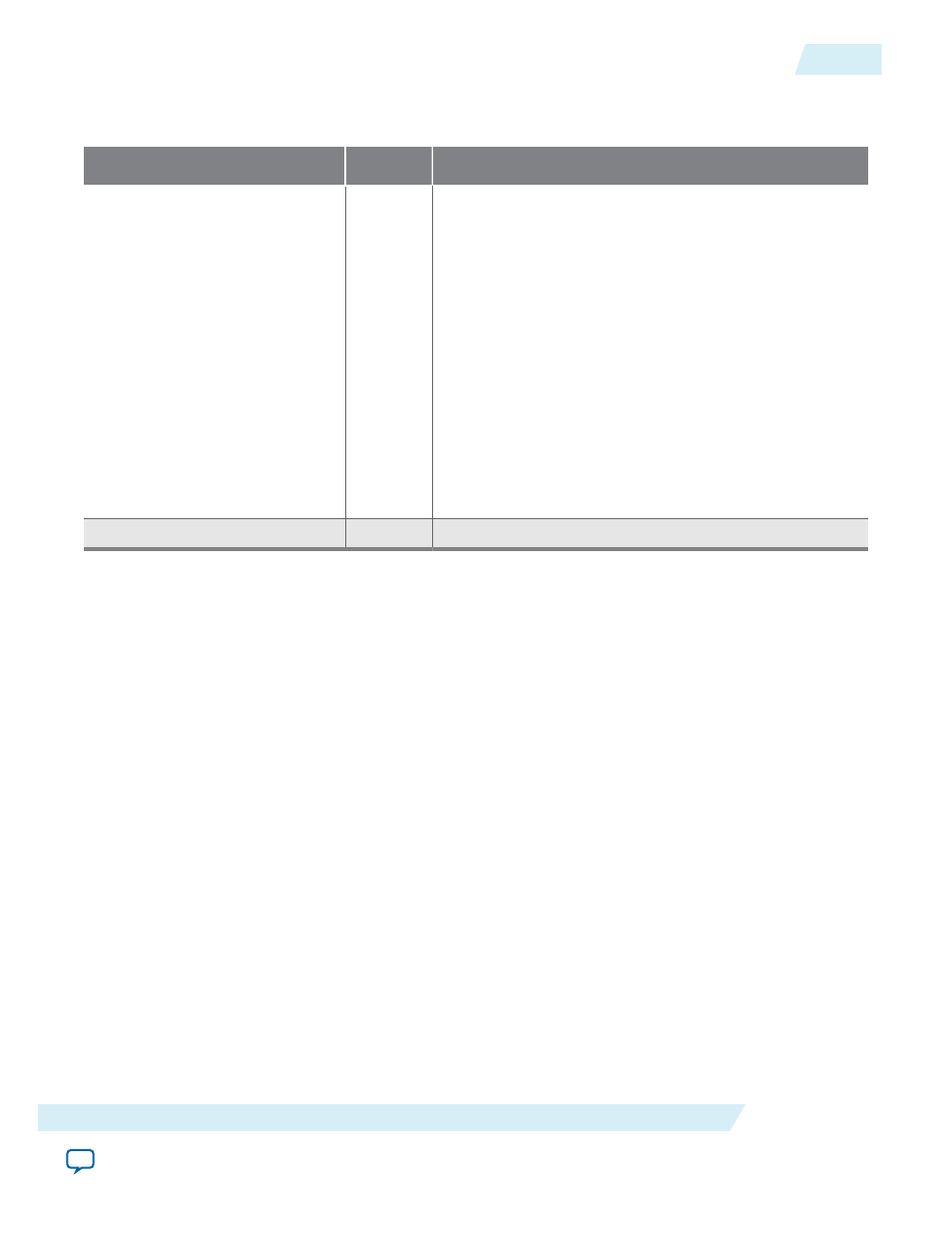

Table 3-14: Auto-Rate Negotiation Control and Status Interface Signals

All interface signals are clocked by the

cpri_clkout

clock.

Signal Name

Direction

Description

nego_bitrate_in[4:0]

Input

CPRI line bit rate to be used in next attempt to achieve

frame synchronization, encoded according to the

following valid values:

• 5'b00001: 0.6144 Gbps

• 5'b00010: 1.2288 Gbps

• 5'b00100: 2.4576 Gbps

• 5'b00101: 3.0720 Gbps

• 5'b01000: 4.9150 Gbps

• 5'b01010: 6.1440 Gbps

• 5'b10000: 9.8304 Gbps

• 5'b10100: 10.1376 Gbps

This signal has higher priority than the

bit_rate

field in

the

BIT_RATE_CONFIG

register at offset 0x0C. When this

signal has the value of 5'b00000, the CPRI v6.0 IP core

responds to the register field.

nego_bitrate_out[4:0]

Output

Reflects the current actual CPRI line bit rate.

Related Information

Extended Delay Measurement

The CPRI v6.0 IP core uses a dedicated clock,

ex_delay_clk

, to measure the delay through the RX and

TX internal buffers to your desired precision. The extended delay process is identical for the two

directions of flow through the IP core; the

TX_EX_DELAY

and

RX_EX_DELAY

registers hold the same

information for the two directions.

The

tx_msrm_period

field of the

TX_EX_DELAY

register contains the value N, such that N clock periods of

the

ex_delay_clk

clock are equal to some whole number M of

cpri_clkout

periods. For example, N

may be a multiple of M, or the M/N frequency ratio may be slightly greater than 1, such as 64/63 or

128/127. The application layer specifies N to ensure the accuracy your application requires. The accuracy

of the Tx buffer delay measurement is N/least_common_multiple(N,M)

cpri_clkout

periods.

Similarly, the

rx_msrm_period

field of the

RX_EX_DELAY

register contains the value N, such that N clock

periods of the

ex_delay_clk

clock are equal to some whole number M of

cpri_clkout

periods.

If your application does not require this precision, drive the

ex_delay_clk

input port with the

cpri_clkout signal. In this case, the M/N ratio of 1 because the frequencies are the same.

The

tx_buf_delay

field of the

TX_DELAY

register indicates the number of 32-bit words currently in the Tx

buffer. After you program the

tx_msrm_period

field of the

TX_EX_DELAY

register with the value of N, the

tx_ex_delay

field of the

TX_EX_DELAY

register holds the current measured delay through the Tx buffer.

The unit of measurement is

cpri_clkout

periods. The

tx_ex_delay_valid

field indicates that a new

measurement has been written to the

tx_ex_delay

field since the previous register read. The following

UG-01156

2014.08.18

Extended Delay Measurement

3-41

Functional Description

Altera Corporation