Altera CPRI v6.0 MegaCore Function User Manual

Page 9

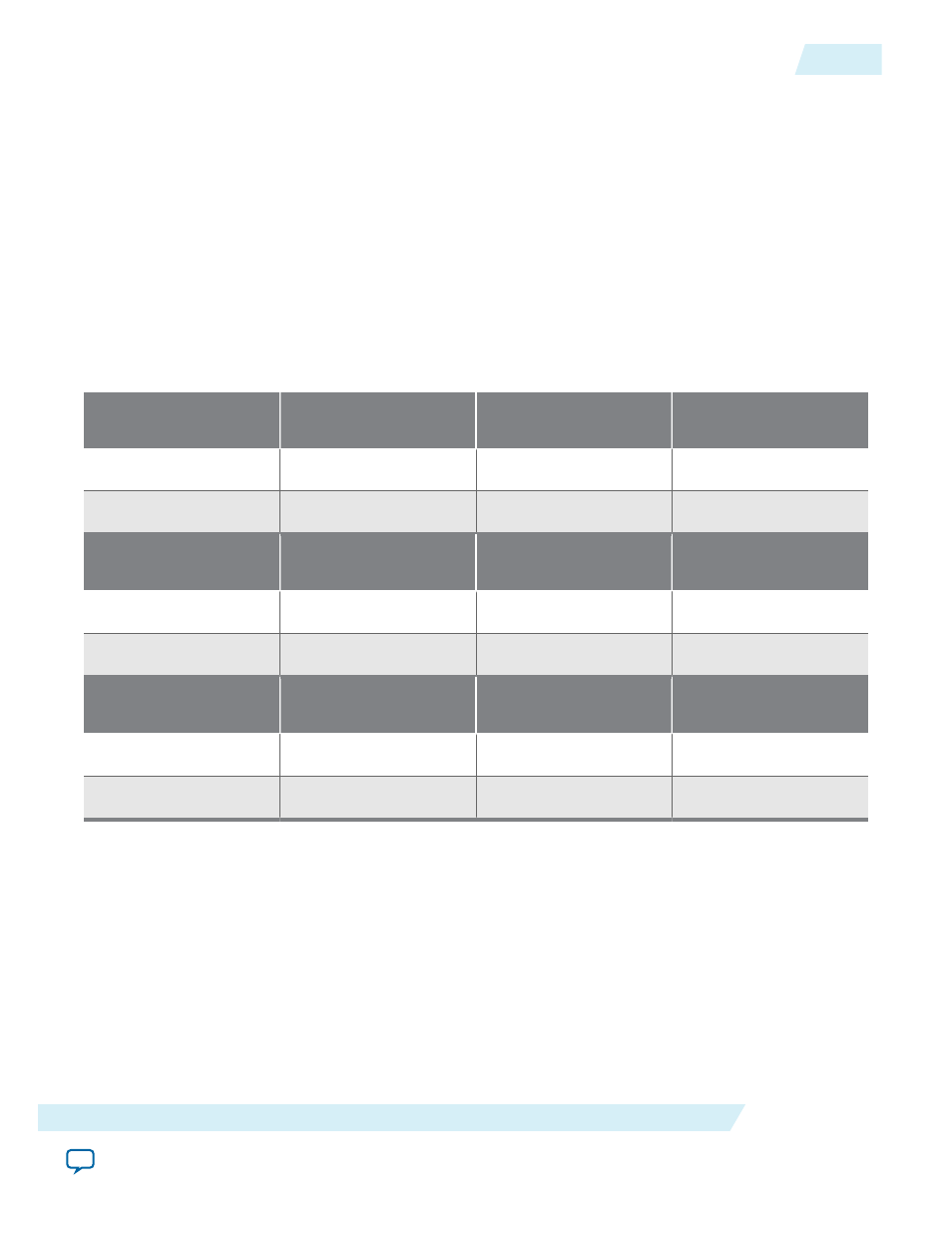

Table 1-4: IP Core FPGA Resource Utilization

Lists the resources and expected performance for selected variations of the CPRI v6.0 IP core in an Arria 10

(10AX115R2F40I2LG), Stratix V (5SGSMD4E2H29C2), or Arria V GZ (5AGZME5K2F40C3) device. All

variations are in Master Operation mode and have a Receiver FIFO depth value of 6.

• Minimum IP core variation: includes no direct interfaces and no L2 interface, supports no loopback mode and

no debug features.

• Maximum IP core variation: includes all direct interfaces and the L2 Ethernet interface, supports all loopback

modes and debug features, has an L2 Ethernet buffer depth parameter value of 7, and an Auxiliary latency

cycle(s) value of 0.

These results were obtained using the Quartus II v14.0 and Quartus II v14.0 Arria 10 Edition software

• The numbers of ALMs and logic registers are rounded up to the nearest 100.

• The numbers of ALMs, before rounding, are the ALMs needed numbers from the Quartus II Fitter Report.

Arria 10 10.3176 Gbps

Variation

ALMs

Logic Registers

M20K Blocks

Minimum

600

1200

4

Maximum

2900

3700

16

Stratix V 10.3176 Gbps

Variation

ALMs

Logic Registers

M20K Blocks

Minimum

700

1300

4

Maximum

3300

4100

18

Arria V GZ 9.8 Gbps

Variation

ALMs

Logic Registers

M20K Blocks

Minimum

800

1300

2

Maximum

2900

3800

13

Related Information

Information about Quartus II resource utilization reporting, including ALMs needed.

UG-01156

2014.08.18

Resource Utilization for CPRI v6.0 IP Cores

1-5

About the CPRI v6.0 IP Core

Altera Corporation