Direct hdlc serial interface, Direct hdlc serial interface -27 – Altera CPRI v6.0 MegaCore Function User Manual

Page 57

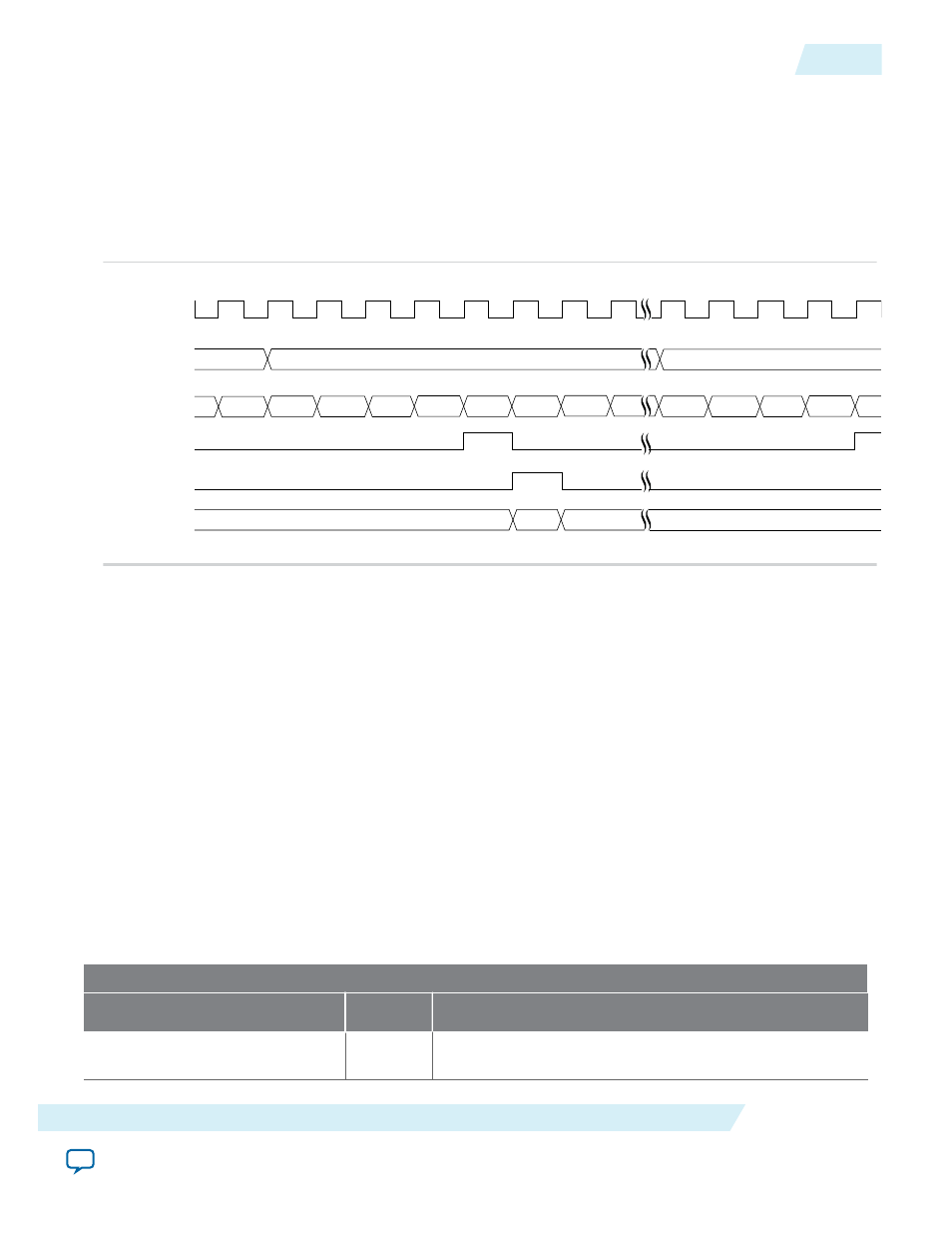

Figure 3-19: Direct RTVS TX Timing Diagram

Expected behavior on the direct RTVS TX interface of a CPRI v6.0 IP core running at 10.1376 Gbps.

The

aux_tx_x

and

aux_tx_seq

signals are not part of this interface and are available only if you turn on

the AUX interface in your CPRI v6.0 IP core variation. However, their presence in the timing diagram

explains the timing of the

rtvs_tx_ready

output signal that you use to identify the clock cycles when you

can write RTVS data to the CPRI frame.

Note that the write latency is one

cpri_clkout

clock cycle in this example.

cpri_clkout

100

101

124

7

4

6

aux_tx_x

aux_tx_seq

rtvs_tx_ready

rtvs_tx_valid

X

D1D2D3D4

X

rtvs_tx_data[31:0]

5

4

3

2

1

0

79

3

2

1

0

Auxiliary latency cycle(s) == 0

Related Information

For more information about the Avalon-ST protocol, including timing diagrams, refer to the Avalon

Streaming Interfaces chapter.

Direct HDLC Serial Interface

If you turn on Enable direct HDLC serial interface in the CPRI v6.0 parameter editor, the direct HDLC

serial interface is available. This interface allows direct access to the slow control and management data in

the CPRI frame. You can connect this interface to a user-defined HDLC PCS and MAC.

This interface is Avalon-ST compliant with a read latency value of 1.

You can alter the transmit write latency with the Auxiliary latency cycle(s) parameter. However, you do

not need to view the

aux_tx_seq

signal for correct alignment. You can monitor the

hdlc_rx_valid

and

hdlc_tx_ready

signals to discover the correct times to read and write data on this interface.

Table 3-9: Direct HDLC Serial Interface Signals

All interface signals are clocked by the

cpri_clkout

clock.

Direct HDLC Serial RX Interface

Signal Name

Direction

Description

hdlc_rx_valid

Output

When asserted, indicates

hdlc_rx_data

holds a valid

HDLC bit in the current clock cycle.

UG-01156

2014.08.18

Direct HDLC Serial Interface

3-27

Functional Description

Altera Corporation