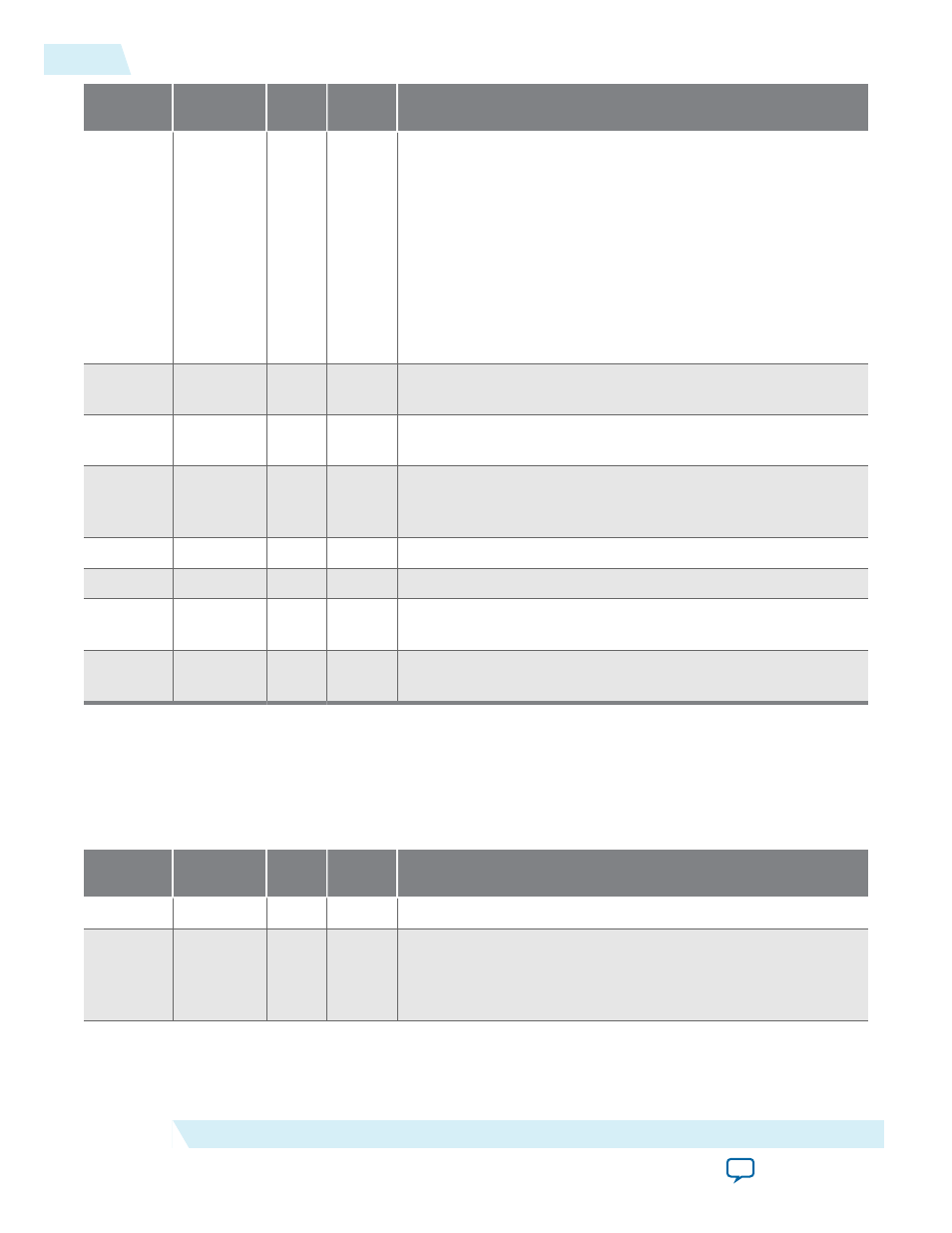

L1_config register, L1_config register -4 – Altera CPRI v6.0 MegaCore Function User Manual

Page 93

Bits

Field Name

Type

Value on

Reset

Description

11

rx_freq_

alarm_

hold

RC

1'b0

CPRI receive clock is not synchronous with main IP core clock

(

cpri_clkout

). This alarm is asserted each time mismatches

are found between the recovered CPRI receive clock and

cpri_

clkout

, and remains asserted until cleared by user logic.

#nik1411442180153/fn_RC_init_reminder

If you turn on Enable debug interface in the CPRI v6.0

parameter editor, the original asynchronous pulse that sets this

register field is vislble on the

rx_freq_alarm

output signal.

However, that signal is not available if you turn off Enable

debug interface.

10

rx_los_

hold

RC

1'b0

Hold

rx_los

.

#nik1411442180153/fn_RC_init_reminder

9

rx_err_

hold

RC

1'b0

Hold

rx_err

.

#nik1411442180153/fn_RC_init_reminder

8

rx_

hfnsync_

hold

RC

1'b0

Hold

rx_hfnsync

.

#nik1411442180153/fn_RC_init_reminder

7:3

Reserved

UR0

5'b0

2

rx_los

RC

1'b0

Indicates receiver is in LOS state.

1

rx_err

RC

1'b0

Indicates 8B10B LCV or 64B/66aB sync header violations

detected.

0

rx_

hfnsync

RC

1'b0

Indicates receiver has achieved hyperframe synchronization

state (HFNSYNC).

L1_CONFIG Register

Table 5-5: CPRI v6.0 IP Core L1_CONFIG Register at Offset 0x08

Bits

Field Name

Type

Value on

Reset

Description

31:4

Reserved

UR0

28'b0

3

tx_ctrl_

insert_en

RW

1'b0

Master enable for insertion of control transmit table entries in

CPRI hyperframe. This signal enables control bytes for which

the

CTRL_INDEX

register

tx_control_insert

bit is high to be

written to the CPRI frame.

5-4

L1_CONFIG Register

UG-01156

2015.02.16

Altera Corporation

CPRI v6.0 IP Core Registers