Altera CPRI v6.0 MegaCore Function User Manual

Page 22

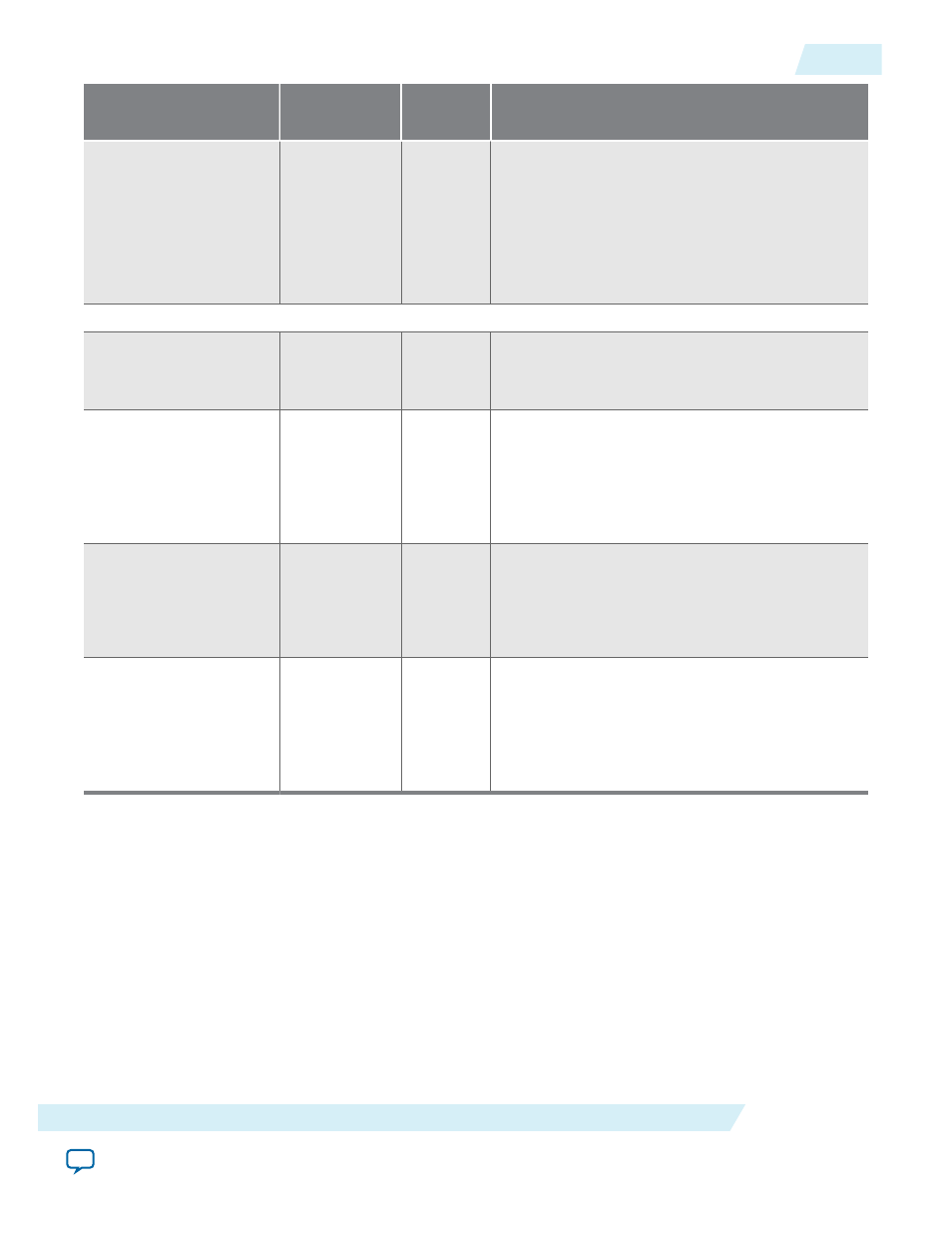

Parameter

Range

Default

Setting

Parameter Description

L2 Ethernet PCS Tx/

Rx FIFO depth

7, 8, 9, 10

7

The value you specify for this parameter is log

2

of

the IP core Layer 2 Ethernet PCS Rx buffer depth

and Tx buffer depth. The IP core supports a

maximum Layer 2 Ethernet PCS buffer depth of

1024.

This parameter is available when you turn on

Enable IEEE 802.3 100BASE-X 100Mbps MII.

Debug Features

Enable debug

interface

• On

• Off

Off

Turn on this parameter to include dedicated

transceiver status and L1 Rx status interfaces to

support debug.

Enable transceiver

PMA forward

loopback path (Tx to

Rx)

• On

• Off

Off

Turn on this parameter to enable transceiver

PMA serial forward loopback. To turn on

transceiver PMA serial forward loopback, you

must also write the value of 2'b01 to the

loop_

forward

field of the

LOOPBACK

register at offset

0x44.

Enable forward

loopback path (Tx to

Rx)

• On

• Off

Off

Turn on this parameter to enable other internal

parallel forward loopback paths. To turn on

internal parallel forward loopback, you must also

write a non-zero value to the

loop_forward

field

of the

LOOPBACK

register at offset 0x44.

Enable reverse

loopback path (Rx to

Tx)

• On

• Off

Off

Turn on this parameter to enable internal parallel

reverse loopback. To turn on reverse loopback,

you must also write a non-zero value to the

loop_

reversed

field of the

LOOPBACK

register at offset

0x44, to specify the parts of the CPRI frame that

are sent on the loopback path.

Related Information

Integrating Your IP Core in Your Design: Required External Blocks

You must connect your CPRI v6.0 IP core to some additional required design components. Your design

can compile without some of these connections and logical blocks, but it will not function correctly in

hardware unless all of them are present and connected in your design.

UG-01156

2014.08.18

Integrating Your IP Core in Your Design: Required External Blocks

2-11

Getting Started with the CPRI v6.0 IP Core

Altera Corporation