Intr register, L1_status register, Intr register -3 – Altera CPRI v6.0 MegaCore Function User Manual

Page 92: L1_status register -3

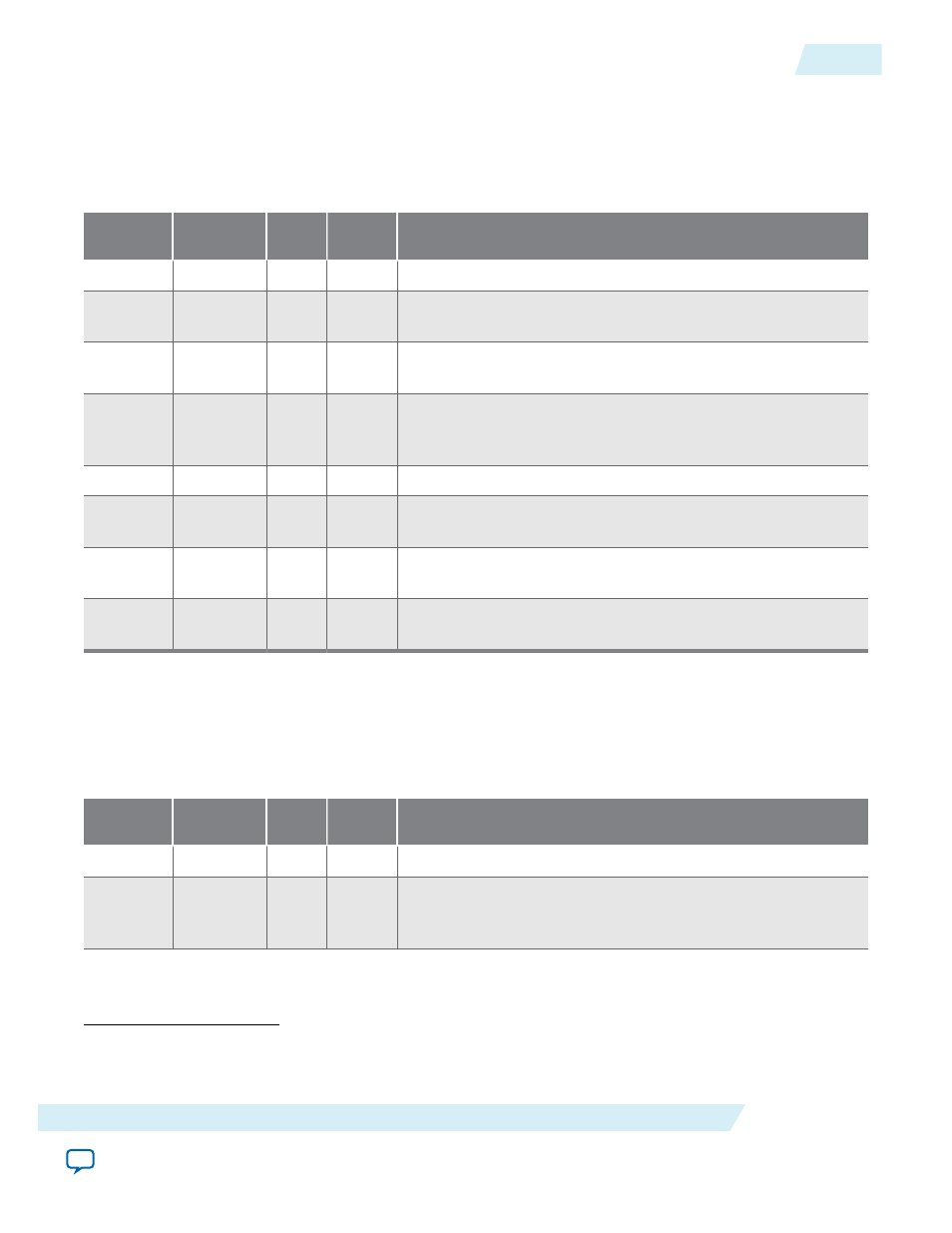

INTR Register

Table 5-3: CPRI v6.0 IP Core INTR Register at Offset 0x00

Bits

Field Name

Type

Value on

Reset

Description

31:19

Reserved

UR0

13'b0

18

intr_sdi_

pending

RW

1'b0

Indicates a remote SDI detected interrupt is not yet serviced

17

intr_rai_

pending

RW

1'b0

Indicates a remote RAI detected interrupt is not yet serviced

16

intr_

reset_

pending

RW

1'b0

Indicates a remote reset request or acknowledge interrupt is not

yet serviced

15:3

Reserved

UR0

13'b0

2

intr_sdi_

en

RW

1'b0

Z.130.0 remote SDI detected interrupt enable

1

intr_rai_

en

RW

1'b0

Z.130.0 remote RAI detected interrupt enable

0

intr_

reset_en

RW

1'b0

Z.130.0 remote reset request or acknowledge received interrupt

enable

L1_STATUS Register

Table 5-4: CPRI v6.0 IP Core L1_STATUS Register at Offset 0x04

Bits

Field Name

Type

Value on

Reset

Description

31:13

Reserved

UR0

19'b0

12

rx_rfp_

hold

RC

1'b0

Radio frame pulse received. This bit is asserted every 10 ms and

remains asserted until cleared by user

logic.

#nik1411442180153/fn_RC_init_reminder

(2)

This register field is a read-to-clear field. You must read the register twice to read the true value of the

field after frame synchronization is achieved. If you observe this bit asserted during link initialization,

read the register again after link initialization to confirm any errors.

UG-01156

2015.02.16

INTR Register

5-3

CPRI v6.0 IP Core Registers

Altera Corporation