Altera CPRI v6.0 MegaCore Function User Manual

Page 29

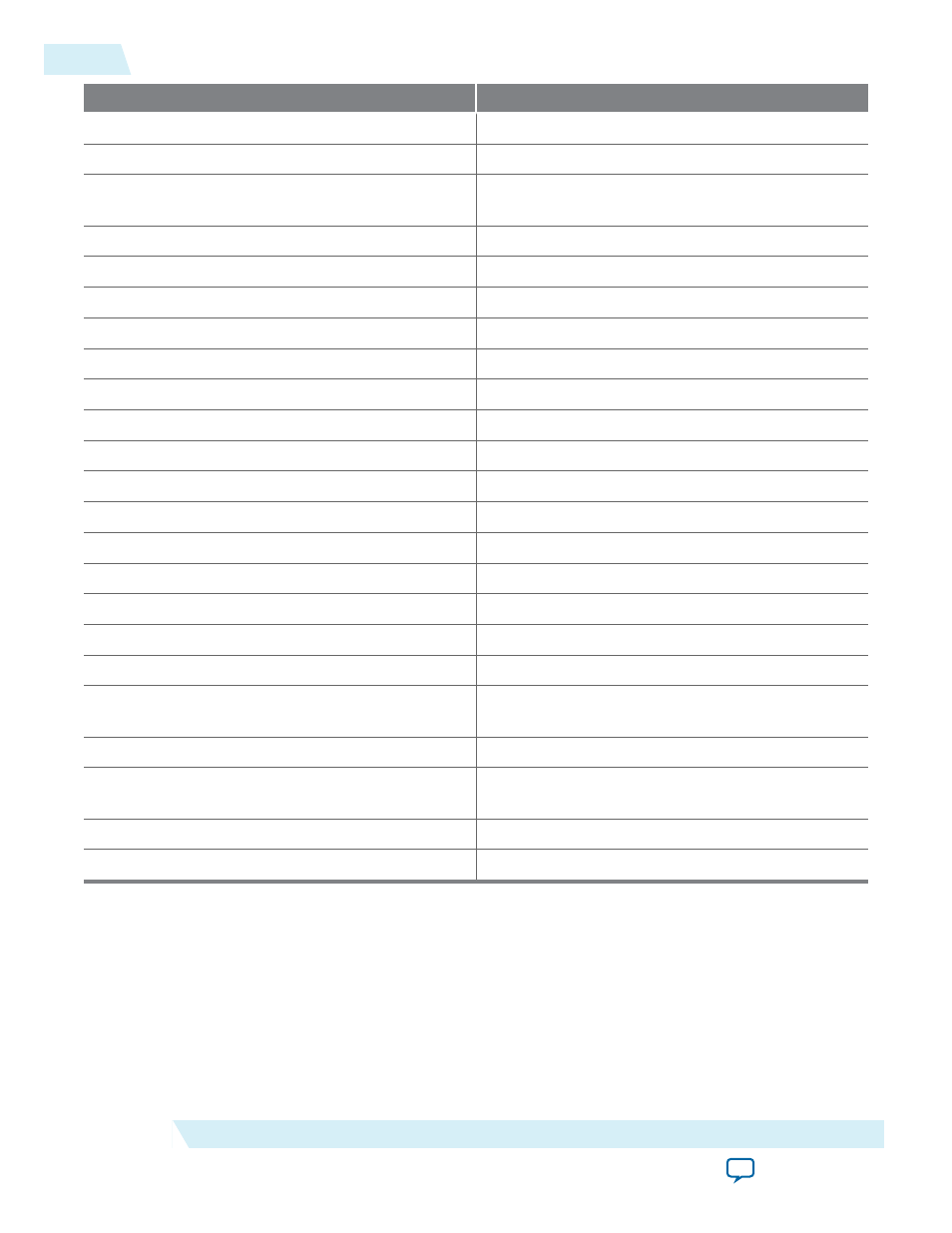

Parameter

Value

Operation mode

Master

Supported receiver CDR frequency (MHz)

307.2

Receiver FIFO depth (value shown is log2 of actual

depth)

6

Enable auto-rate negotiation

Turn off

Enable auto-rate negotiation down to 614.4Mbps

Not available

Supported CPU interface standard

AvalonMM

Auxiliary latency cycle(s)

0

Enable auxiliary interface

Turn on

Enable all control word access

Turn off

Enable direct IQ mapping interface

Turn off

Enable direct ctrl_axc access interface

Turn on

Enable direct vendor specific access interface

Turn on

Enable start-up sequence state machine

Turn off

Enable L1 inband protocol negotiator

Not available

Enable real-time vendor specific interface (R-16A)

Not available

Enable Z.130.0 access interface

Turn off

Enable direct HDLC serial interface

Turn on

Enable IEEE 802.3 100BASE-X 100Mbps MII

Turn on

L2 Ethernet PCS Tx/Rx FIFO depth (value shown is

log2 of actual depth)

Turn off

Enable debug interface

Turn off

Enable transceiver PMA forward loopback path (Tx

to Rx)

Turn off

Enable forward loopback path (Tx to Rx)

Turn off

Enable reversed loopback path (Rx to Tx)

Turn off

4. In the CPRI v6.0 parameter editor, click the Example Design button and specify the desired location

of the testbench.

5. After you generate the demonstration testbench, in the Quartus II software, click View > Utility

Windows > Tcl Console.

6. In the Tcl Console, change directory to your specified testbench directory's

ip_sim

subdirectory.

7. Type

source gen_sim_verilog.tcl

or

source gen_sim_vhdl.tcl

, depending on the language of

the model you wish to simulate. Running this script generates the DUT and testbench files.

8. If you are using a simulator that requires that you open a user interface, open your target simulator.

2-18

Running the Testbench

UG-01156

2014.08.18

Altera Corporation

Getting Started with the CPRI v6.0 IP Core