Altera CPRI v6.0 MegaCore Function User Manual

Page 58

Direct HDLC Serial RX Interface

Signal Name

Direction

Description

hdlc_rx_data

Output

HDLC data stream received from the CPRI frame. The

hdlc_rx_valid

signal indicates which bits are valid

HDLC bytes.

Direct HDLC Serial TX Interface

Signal Name

Direction

Description

hdlc_tx_ready

Output

When asserted, indicates the IP core is ready to receive

HDLC data from

hdlc_tx_data

on the next clock cycle.

hdlc_tx_valid

Input

Write valid for

hdlc_tx_data

. Assert this signal to

indicate that

hdlc_tx_data

holds a valid HDLC bit in the

current clock cycle.

hdlc_tx_data

Input

HDLC data stream to be written to the CPRI frame

directly. The IP core writes the current value on

hdlc_tx_

data

to the CPRI frame based on the

hdlc_tx_ready

signal from the previous cycle, and the

hdlc_tx_valid

signal in the current cycle.

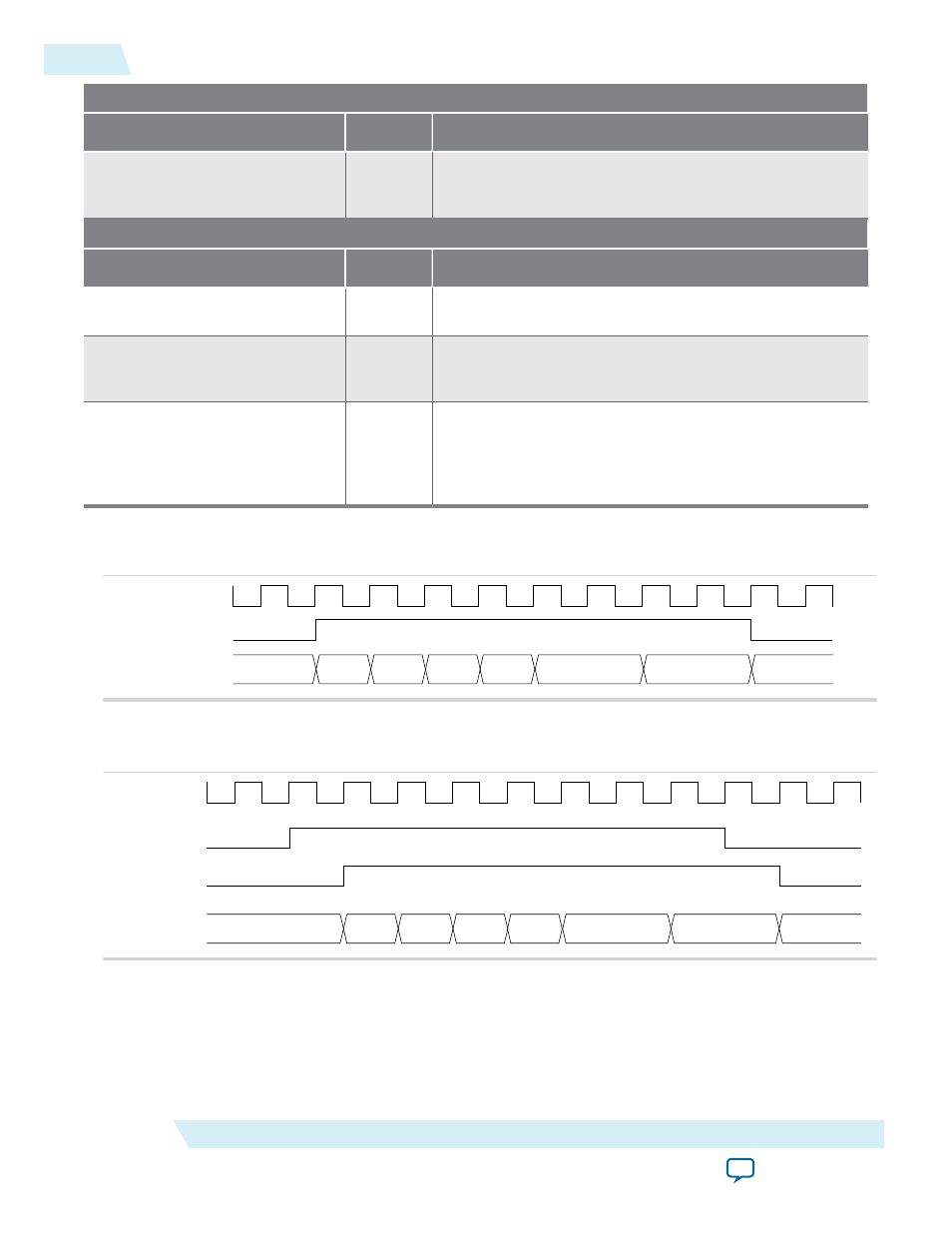

Figure 3-20: Direct HDLC Serial RX Timing Diagram

HDLC Serial RX interface behavior in a CPRI v6.0 IP core running at 0.6144 Gbps.

cpri_clkout

hdlc_rx_ready

1

X

X

0

1

0

1

0

hdlc_rx_data

Figure 3-21: Direct HDLC Serial TX Timing Diagram

Expected behavior on the HDLC Serial TX interface of a CPRI v6.0 IP core running at 0.6144 Gbps.

cpri_clkout

hdlc_tx_ready

hdlc_tx_valid

1

X

X

0

1

0

1

0

hdlc_tx_data

Related Information

For more information about the Avalon-ST protocol, including timing diagrams, refer to the Avalon

Streaming Interfaces chapter.

3-28

Direct HDLC Serial Interface

UG-01156

2014.08.18

Altera Corporation

Functional Description