Cpri link, Cpri link -45 – Altera CPRI v6.0 MegaCore Function User Manual

Page 75

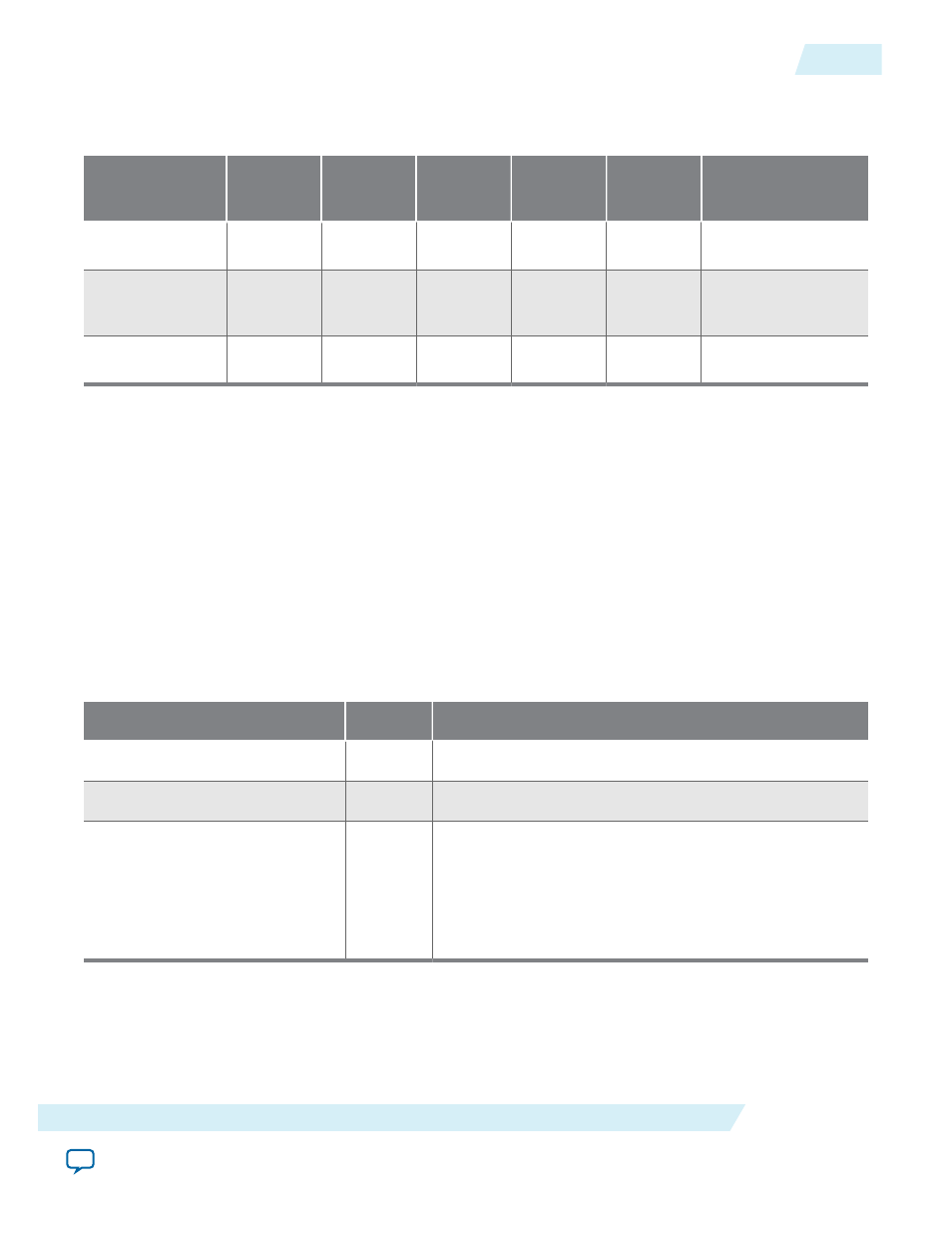

Table 3-21: Delays on Receive Path Through CPRI v6.0 IP Core in Stratix V Devices

In this table, P1 is the duration of one

cpri_clkout

clock cycle, and P2 is the duration of one RX PCS clock cycle.

rx_ex_delay is the value in the

rx_ex_delay

field of the RX_EX_DELAY register at offset 0x54.

CPRI Line Bit Rate

(Gbps)

Bits per

cpri_clkout

Cycle

Bits per RX

PCS Clock

Cycle (=B2)

Through

PMA

Through

PCS

Through RX

Buffer

From RX Buffer to AUX

RX Interface

0.6144

32

10

(2 x P2) +

(6 x P2/B2)

8 x P2

rx_ex_delay (7 x P1) + P2

1.2288–9.8304 32

40

31 x P2/B2 (6 x P2) +

(20 x P2/

B2)

rx_ex_delay 8 x P1

10.1376

32

40

31 x P2/B2 9 x P2

rx_ex_delay

x 2

(7 x P1) + P2

CPRI v6.0 IP Core Transceiver and Transceiver Management Interfaces

The CPRI v6.0 IP core configures the interface to the CPRI serial link in an Altera device transceiver

channel. The IP core provides multiple interfaces for managing the transceiver. The transceiver is

configured with a Native PHY IP core and exposes many of its optional interfaces for ease of IP core

integration in your design.

CPRI Link

The CPRI v6.0 IP core configures the interface to the CPRI serial link in an Altera device transceiver

channel.

Table 3-22: CPRI Link Interface Signals

Signal Name

Direction

Description

xcvr_rxdatain

Input

High-speed serial data receiver port.

xcvr_txdataout

Output

High-speed serial data transmitter port.

xcvr_los

Input

Asynchronous signal that forces link to LOS state for

quick resynchronization.

If you implement the CPRI link with a fiber optic channel,

you could connect this input signal to the SFP module

LOS signal so that it is asserted when the SFP module loses

signal.

UG-01156

2014.08.18

CPRI v6.0 IP Core Transceiver and Transceiver Management Interfaces

3-45

Functional Description

Altera Corporation