Altera CPRI v6.0 MegaCore Function User Manual

Page 111

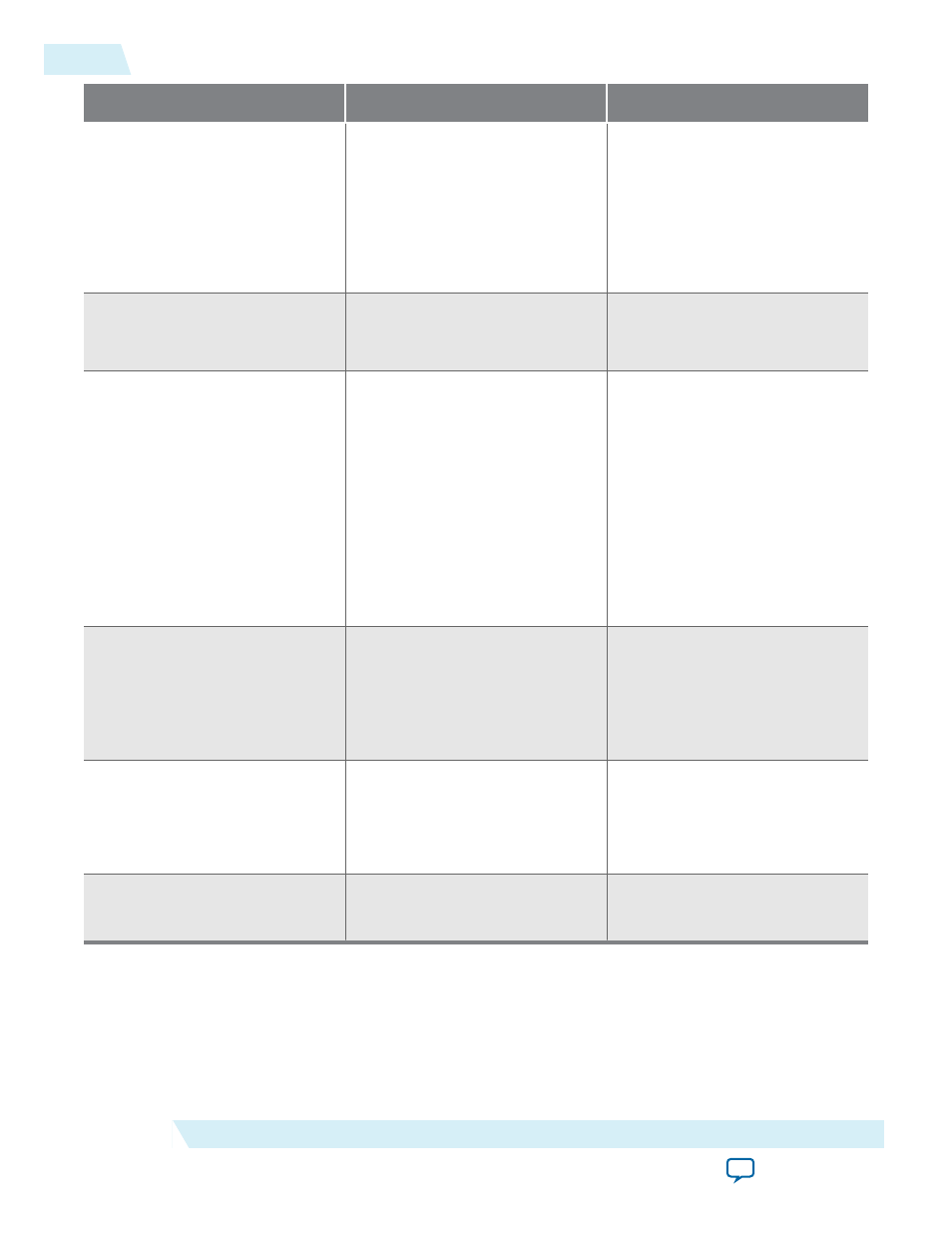

Property

CPRI v6.0 IP Core (Initial Release)

CPRI IP Core

Ethernet MAC

Includes Ethernet PCS block that

communicates with user logic

through an IEEE 802.3 100BASE-X

100Mbps MII.

Optionally includes an Ethernet

MAC block that communicates

with user logic through registers.

If you do not include the

Ethernet MAC, user logic can

communicate with the internal

Ethernet PCS block through an

MII-like interface.

HDLC

Supports optional HDLC serial

direct connection to Layer 1.

Optionally includes an HDLC

block that communicates with

user logic through registers.

Direct access to CPRI frame

Supports AUX interface for direct

access to full CPRI frame, with

optional specified latency. Also

supports individual interfaces for

direct access to I/Q data bytes only,

to Ctrl-AxC bytes only, to VSS bytes

only, and for 10.1376 Gbps

variations, to RTVS bytes only. You

can configure any combination of

these interfaces.

Optionally supports register access

to all control words in CPRI frame.

Supports AUX interface for

direct access to full CPRI frame.

Optionally supports register

access to all control words in

CPRI frame.

I/Q Mapping

Supports direct IQ interface to

access the I/Q bytes in the CPRI

frame.

Optionally includes an I/Q

mapper that supports certain

wireless standards. For direct

access to IQ data in the CPRI

frame, only the AUX interface is

available.

Start-Up Sequence State

Machine

Optionally includes a state machine

that controls the start-up sequence.

Optionally includes negotiation of

protocol version and Layer 2

Control and Management rates.

Requires that software control

start-up sequence, including

negotiation of protocol version

and Layer 2 Control and

Management rates.

Debug and Alarm Signals

Optional additional debug interface

and optional interface for access to

all five Z.130.0 alarms.

Signals to control and monitor

Z.130.0 reset requests.

Related Information

•

For detailed information about changes to top-level interfaces in different versions of the legacy CPRI

IP core, refer to the Document Revision History in the Additional Information chapter.

A-2

Differences Between CPRI v6.0 IP Core and CPRI IP Core

UG-01156

2014.08.18

Altera Corporation

Differences Between CPRI v6.0 IP Core and CPRI IP Core