Interface to the external pll, Interface to the external pll -48 – Altera CPRI v6.0 MegaCore Function User Manual

Page 78

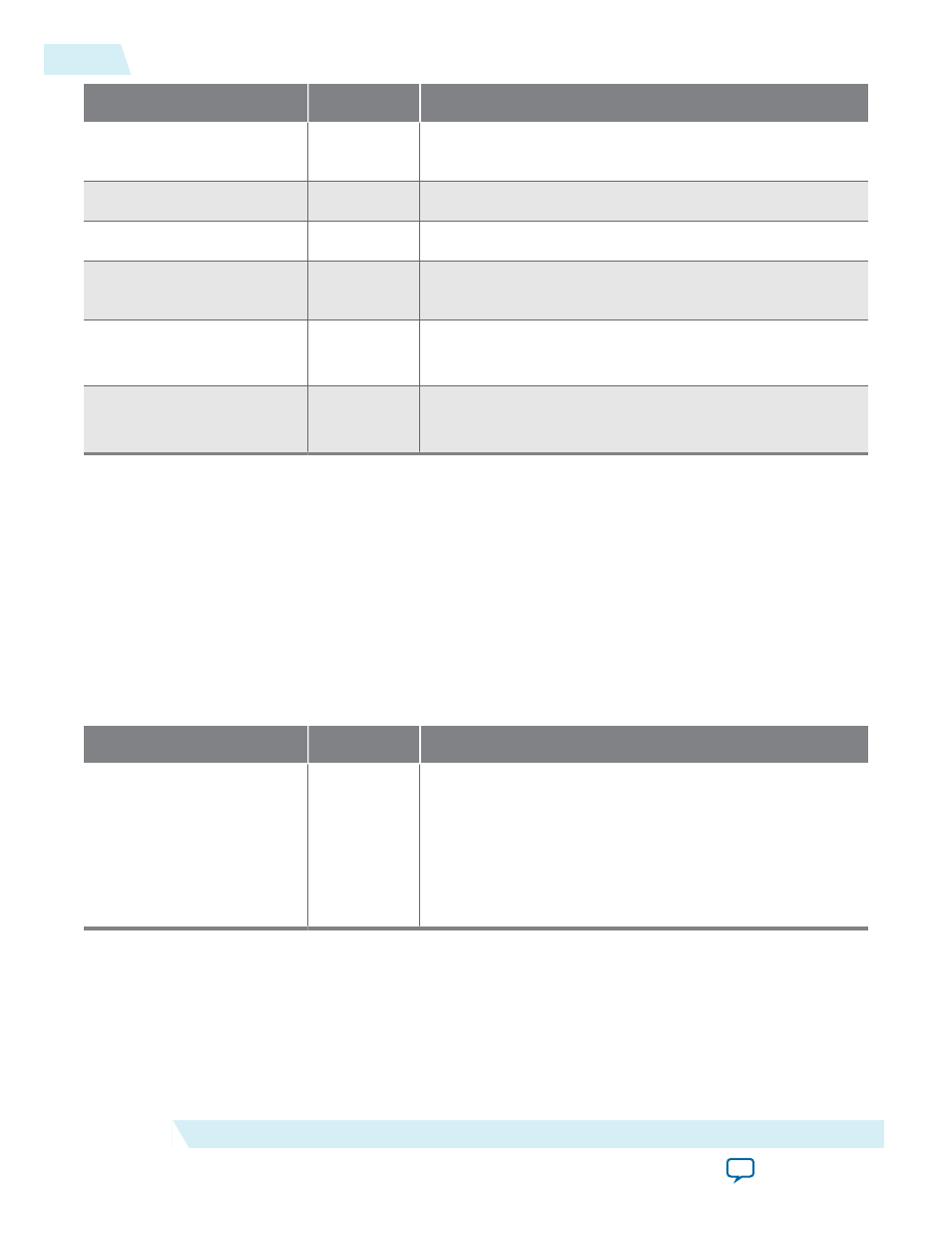

Signal Name

Direction

Description

xcvr_tx_cal_busy

Output

Indicates to external reset controller that the transmitter is

still busy with the calibration process.

xcvr_rx_analogreset

Input

Analog reset to receiver from external reset controller.

xcvr_rx_digitalreset

Input

Digital reset to receiver from external reset controller.

xcvr_rx_cal_busy

Output

Indicates to external reset controller that the receiver is still

busy with the calibration process.

xcvr_reset_tx_ready

Input

Indicates the Tx reset controller reset sequence is

completed. When this signal is asserted, the IP core begins a

reset of the IP core Tx path.

xcvr_reset_rx_ready

Input

Indicates the Rx reset controller reset sequence is

completed. When this signal is asserted, the IP core begins a

reset of the IP core Rx path.

Related Information

Adding the External Reset Controller

Information about the Altera Transceiver Reset Controller IP core for Arria V GZ and Stratix V devices.

Information about the Altera Transceiver Reset Controller IP core for Arria 10 devices.

Interface to the External PLL

Table 3-27: CPRI v6.0 IP Core External PLL Interface Signals

The CPRI v6.0 IP core requires that you generate and connect an external transceiver PLL IP core.

Signal Name

Direction

Description

xcvr_ext_pll_clk

Input

Clocks the transmitter PMA.

You should drive this input clock with the output of the

external transceiver TX PLL. In Arria 10 devices, you have a

choice of different TX PLL IP cores to configure. You must

ensure that you configure a PLL IP core that is capable of

driving the frequency that the CPRI v6.0 IP core requires to

run at the specified CPRI line bit rate.

Related Information

Information about the Arria V GZ and Stratix V transceiver PLL IP cores.

Information about the Arria 10 transceiver PLL IP cores.

3-48

Interface to the External PLL

UG-01156

2014.08.18

Altera Corporation

Functional Description