Altera CPRI v6.0 MegaCore Function User Manual

Page 34

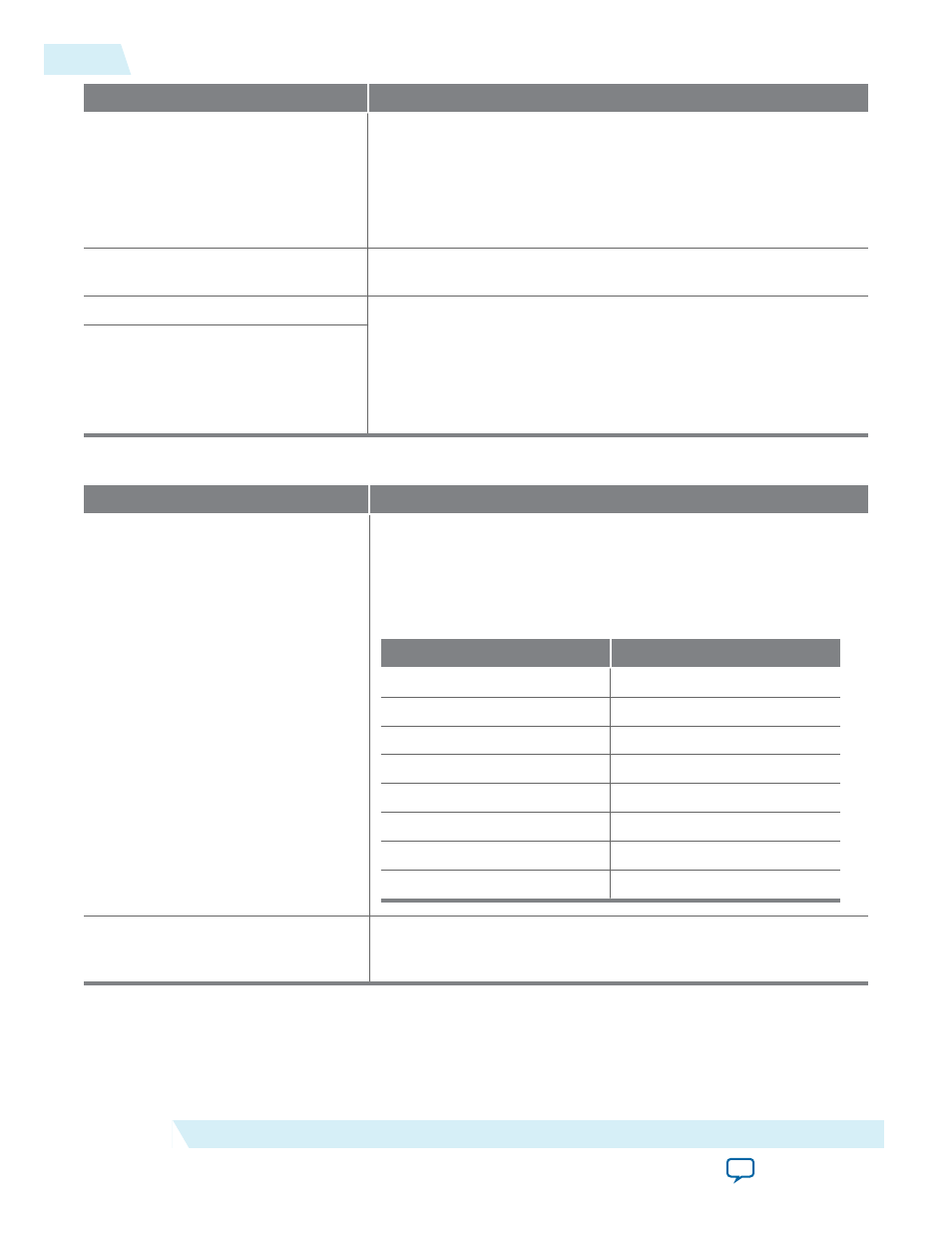

CPRI v6.0 Input Clock

Information

cpri_10g_coreclk

Drives the CPRI v6.0 IP core clock

cpri_clkout

when the IP core

is running at the CPRI line bit rate of 10.1376 Gbps.

You must drive this clock at 307.20 MHz.

You must drive this clock from the same clock source as the

xcvr_

ext_pll_clk

input signal to the IP core.

cpu_clk

Clocks the signals on the CPRI v6.0 CPU interface. Supports any

frequency that the device fabric supports.

mii_txclk

mii_txclk

clocks the MII transmitter interface and

mii_rxclk

clocks the MII receiver interface. You must drive these clocks at the

frequency of 25 MHz to achieve the 100 Mbps bandwidth required

for this interface.

These clocks are present only if you turn on Enable IEEE 802.3

100BASE-X 100Mbps MII in the CPRI v6.0 parameter editor.

mii_rxclk

Table 3-2: CPRI v6.0 IP Core Output Clocks

CPRI v6.0 Output Clock

Information

cpri_clkout

Master clock for the CPRI v6.0 IP core. When the IP core is

running at the CPRI line bit rate of 10.1376 Gbps, the

cpri_10g_

coreclk

input clock drives

cpri_clkout

. At all other CPRI line bit

rates, the Tx PCS drives

cpri_clkout

.

The frequency of

cpri_clkout

depends on the CPRI line bit rate:

CPRI Line Bit Rate

cpri_clkout

Frequency

0.6144 Gbps

15.36 MHz

1.2288 Gbps

30.72 MHz

2.4576 Gbps

61.44 MHz

3.0720 Gbps

76.80 MHz

4.9152 Gbps

122.88 MHz

6.1440 Gbps

153.60 MHz

9.8304 Gbps

245.76 MHz

10.1376 Gbps

307.20 MHz

xcvr_recovered_clk

Direct recovered clock from the receiver CDR. Use this output

clock to drive the external clean-up PLL when your IP core is in

slave mode.

Related Information

3-4

CPRI v6.0 IP Core Clocking Structure

UG-01156

2014.08.18

Altera Corporation

Functional Description