Cpri v6.0 ip core clocking structure, Cpri v6.0 ip core clocking structure -3 – Altera CPRI v6.0 MegaCore Function User Manual

Page 33

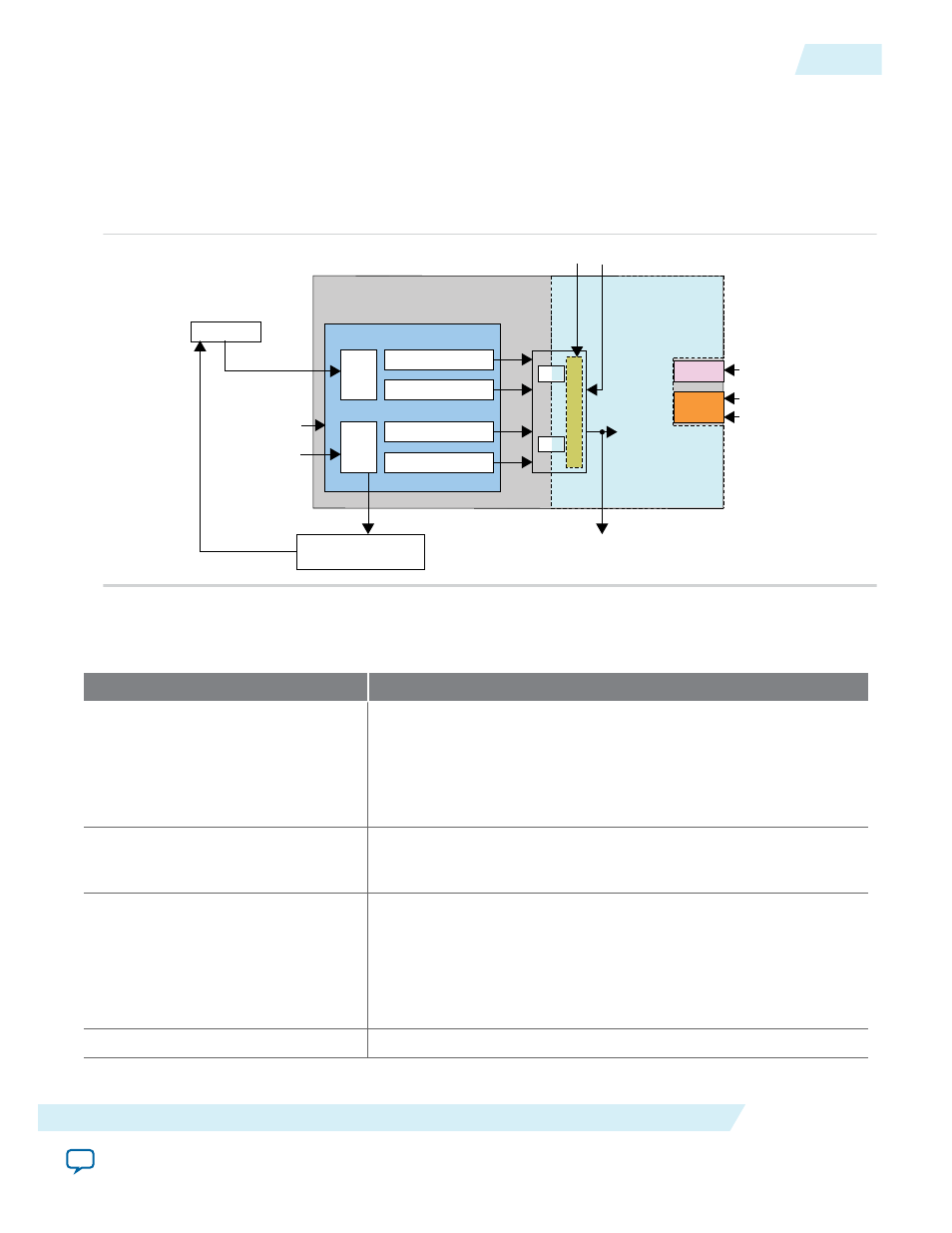

CPRI v6.0 IP Core Clocking Structure

Figure 3-2: CPRI v6.0 IP Core Clocking Structure

Illustrates the clocks and clock domains in the CPRI v6.0 IP core. Clock domains shown are

cpri_clkout

,

clk_ex_delay

,

cpu_clk

, and

mii_{rx,tx}clk

. The external clean-up PLL is only required in slave

clocking mode.

TX PLL

Standard TX PCS

10G TX PCS

TX

PMA

Standard RX PCS

10G RX PCS

RX

PMA

Native PHY IP Core

CPRI v6.0 IP Core

cpu_clk

mii_rxclk

mii_txclk

clk_ex_delay

cpri_10g_coreclk

reconfig_clk

xcvr_ext_pll_clk

xcvr_recovered_clk

xcvr_cdr_refclk

cpri_clkout

External Clean-Up PLL

(in slave mode only)

CPU Interface

Ex

tended D

ela

y Measur

emen

t

MII

FIFO

FIFO

The main CPRI v6.0 IP core clock is

cpri_clkout

.

Table 3-1: CPRI v6.0 IP Core Input Clocks

CPRI v6.0 Input Clock

Information

xcvr_ext_pll_clk

Clocks the transmitter PMA.

You should drive this input clock with the output of the external TX

PLL. In Arria 10 devices, the frequency of this clock must be one

half the CPRI line bit rate. You must configure a PLL IP core that is

capable of driving the required frequency.

xcvr_cdr_refclk

Receiver CDR reference clock. You must drive this clock at the

frequency you specified for the Supported receiver CDR frequency

(MHz) parameter in the CPRI v6.0 parameter editor.

reconfig_clk

In Stratix V and Arria V GZ variations, clock for CPRI v6.0 IP core

transceiver start-up and reconfiguration.

In Arria 10 variations, clocks the signals on the CPRI v6.0

transceiver reconfiguration interface.

The supported frequency range of this clock is 100–150 MHz.

ex_delay_clk

Clock for extended delay measurement.

UG-01156

2014.08.18

CPRI v6.0 IP Core Clocking Structure

3-3

Functional Description

Altera Corporation