Main transceiver clock and reset signals, Arria 10 transceiver reconfiguration interface, Main transceiver clock and reset signals -46 – Altera CPRI v6.0 MegaCore Function User Manual

Page 76: Arria 10 transceiver reconfiguration interface -46

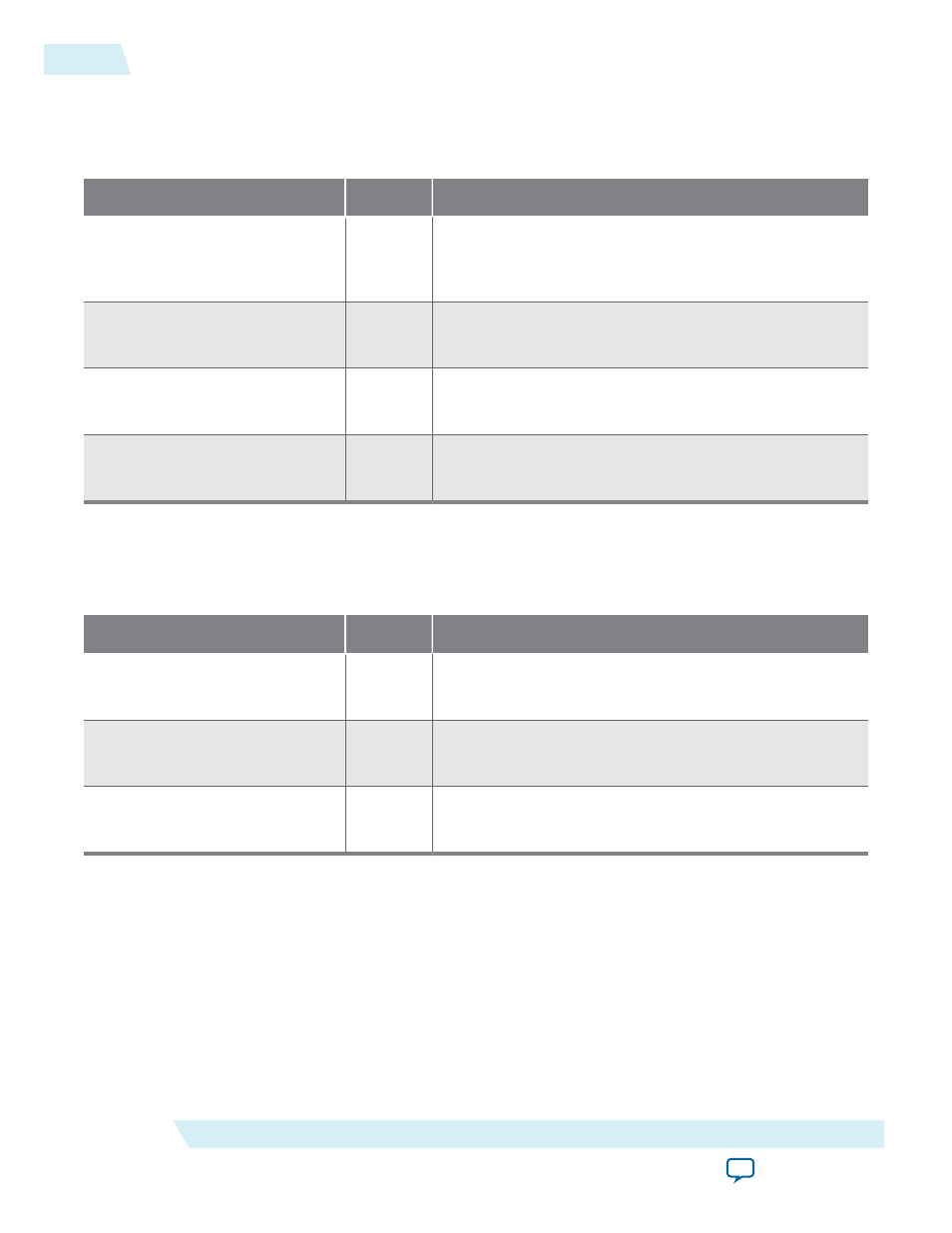

Main Transceiver Clock and Reset Signals

Table 3-23: Main Transceiver Clock and Reset-Done Signals

The clocks for individual interfaces are listed with the relevant interface signals.

Signal Name

Direction

Description

xcvr_cdr_refclk

Input

Receiver CDR reference clock. You must drive this clock

at the frequency you specified for the Supported receiver

CDR frequency (MHz) parameter in the CPRI v6.0

parameter editor.

xcvr_recovered_clk

Output

Direct recovered clock from the receiver CDR. Use this

output clock to drive the external clean-up PLL when your

IP core is in slave mode.

xcvr_reset_tx_done

Output

Indicates the transmitter and IP core Tx path have

completed the internal reset sequence. This signal is

clocked by the

cpri_clkout

clock.

xcvr_reset_rx_done

Output

Indicates the receiver and IP core Rx path have completed

the internal reset sequence. This signal is clocked by the

cpri_clkout

clock.

Arria V GZ and Stratix V Transceiver Reconfiguration Interface

Table 3-24: Arria V GZ and Stratix V Transceiver Reconfiguration Interface Signals

All interface signals are clocked by the

reconfig_clk

clock.

Signal Name

Direction

Description

reconfig_clk

Input

Clock for CPRI v6.0 IP core transceiver start-up and

reconfiguration. The frequency range for this clock is 100–

150 MHz.

reconfig_to_xcvr[69:0]

Input

Parallel transceiver reconfiguration bus from the Altera

Transceiver Reconfiguration Controller to the transceiver

in the CPRI v6.0 IP core.

reconfig_from_xcvr[45:0]

Output

Parallel transceiver reconfiguration bus to the Altera

Transceiver Reconfiguration Controller from the

transceiver in the CPRI v6.0 IP core.

Related Information

Adding the Transceiver Reconfiguration Controller

on page 2-15

Information about the Transceiver Reconfiguration Controller IP core.

Arria 10 Transceiver Reconfiguration Interface

Altera provides a dedicated Avalon-MM interface, called the Arria 10 transceiver reconfiguration

interface, to access the Arria 10 transceiver registers. You access the Arria 10 Native PHY IP core registers

through this dedicated interface and not through the IP core general purpose control and status interface.

This interface provides access to the hard PCS registers on the device.

3-46

Main Transceiver Clock and Reset Signals

UG-01156

2014.08.18

Altera Corporation

Functional Description