Adding the clean-up pll, Adding the clean-up pll -12 – Altera CPRI v6.0 MegaCore Function User Manual

Page 23

The CPRI v6.0 IP core requires that you define, instantiate, and connect the following additional software

and hardware modules for all CPRI v6.0 IP core variations:

• An external PLL IP core to configure the transceiver TX PLL. Although the hardware this IP core

configures is physically part of the device transceiver, you must instantiate it in software separately

from the CPRI v6.0 IP core. In Arria 10 devices, this Altera requirement supports the configuration of

multiple Altera IP cores using the same transceiver block in the device.

• One or more external reset controllers to coordinate the reset sequence for the CPRI v6.0 IP core in

your design.

In addition, CPRI link slave modules require an external clean-up PLL and Arria V GZ and Stratix V

variations require an external transceiver reconfiguration controller.

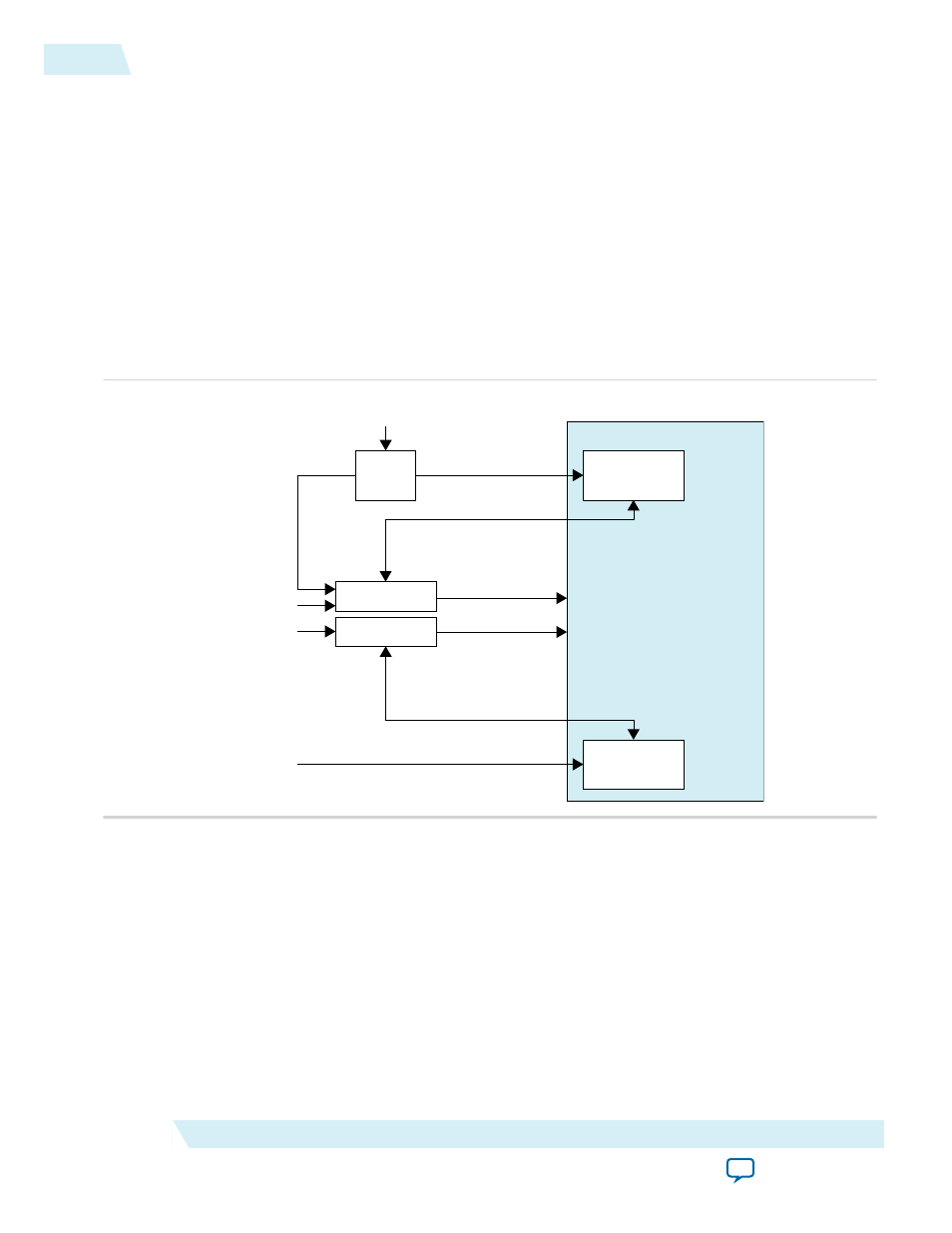

Figure 2-4: Required External Blocks

An example showing how you could connect required components to a single CPRI v6.0 IP core.

Reset Controller

Reset Controller

TX

PLL

Transmitter

(Native PHY)

Receiver

(Native PHY)

User-Defined

Reference Clock

xcvr_ext_pll_clk

xcvr_tx_analogreset

xcvr_tx_digitalreset

xcvr_tx_cal_busy

xcvr_rx_analogreset

xcvr_rx_digitalreset

xcvr_rx_is_lockedtodata

xcvr_rx_cal_busy

xcvr_cdr_refclk

reset_tx

reset_rx

pll_locked

CPRI v6.0 IP Core

xcvr_reset_tx_ready

xcvr_reset_rx_ready

Related Information

Adding the External Reset Controller

Adding the Clean-Up PLL

If your CPRI v6.0 IP core is an RE slave, you must connect it to an external clean-up PLL to clean up any

jitter that occurs in the CDR output clock before sending it to the external TX PLL.

The clean-up PLL performs the clock synchronization necessary to address the CPRI v6.0 Specification

requirements R-17, R-18, and R-18A, which address jitter and frequency accuracy in the RE core clock for

radio transmisstion.

2-12

Adding the Clean-Up PLL

UG-01156

2014.08.18

Altera Corporation

Getting Started with the CPRI v6.0 IP Core