Altfp_log – Altera Floating-Point User Manual

Page 97

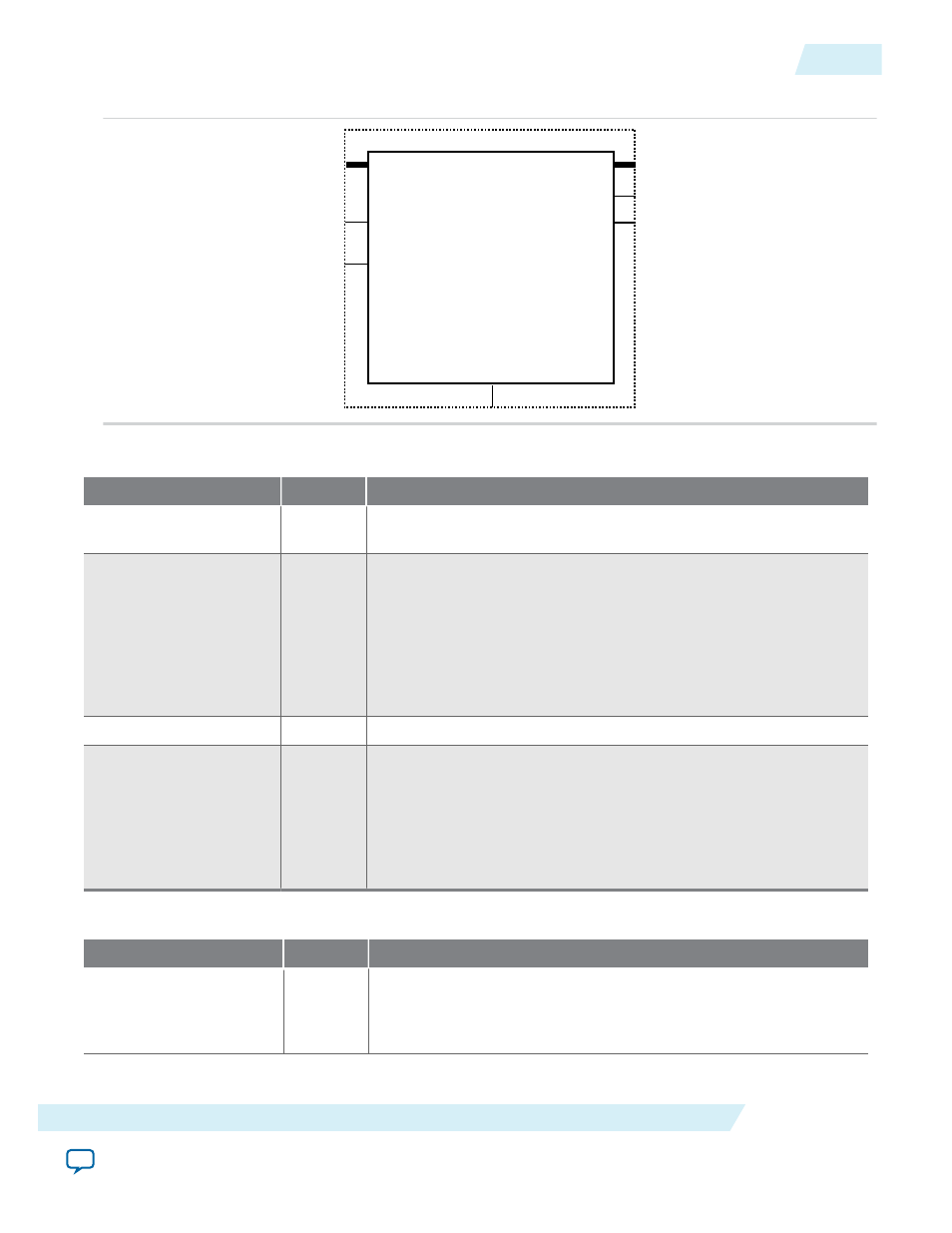

Figure 12-3: ALTFP_LOG Signals

data[]

clk_en

clock

inst

ALTFP_LOG

result[]

zero

nan

aclr

Table 12-5: ALTFP_LOG IP Core Input Signals

Port Name

Required

Description

aclr

No

Asynchronous clear. When the

aclr

port is asserted high, the

function is asynchronously cleared.

clk_en

No

Clock enable. When the

clk_en

port is asserted high, a natural

logarithm operation takes place. When signal is asserted low, no

operation occurs and the outputs remain unchanged.

Deasserting

clk_en

halts operation until it is asserted again. Assert

the

clk_en

signal for the number of clock cycles equivalent to the

required output latency (

PIPELINE

parameter value) for the results

to be shown at the output.

clock

Yes

Clock input to the IP core.

data[]

Yes

Floating-point input data. The MSB is the sign bit, the next MSBs

are the exponent, and the LSBs are the mantissa. This input port size

is the total width of the sign bit, exponent bits, and mantissa bits.

For single precision, the width is fixed to 32 bits. For double

precision, the width is fixed to 64 bits. For single extended

precision, you can choose a width in the range from 43 to 64 bits.

Table 12-6: ALTFP_LOG IP Core Output Signals

Port Name

Required

Description

result[]

Yes

The natural logarithm of the value on input data. The natural

logarithm of the

data[]

input port, shown in floating-point format.

The widths of the

result[]

output port and

data[]

input port are

the same.

UG-01058

2014.12.19

Signals

12-5

ALTFP_LOG

Altera Corporation