Altfp_abs signals, Altfp_abs signals -3 – Altera Floating-Point User Manual

Page 107

In this example, the latency of the multiplier is set to five clock cycles, while none is being set for the

absolute value function. Thus, the absolute value result only appears at the

result[]

port five cycles after

the input values are captured on the input ports.

The

dataa[]

and

datab[]

values in the simulation waveform above portray the two input values that are

being fed to the multiplier. The value in the

result[]

port depicts the multiplication result that has gone

through the absolute value operation.

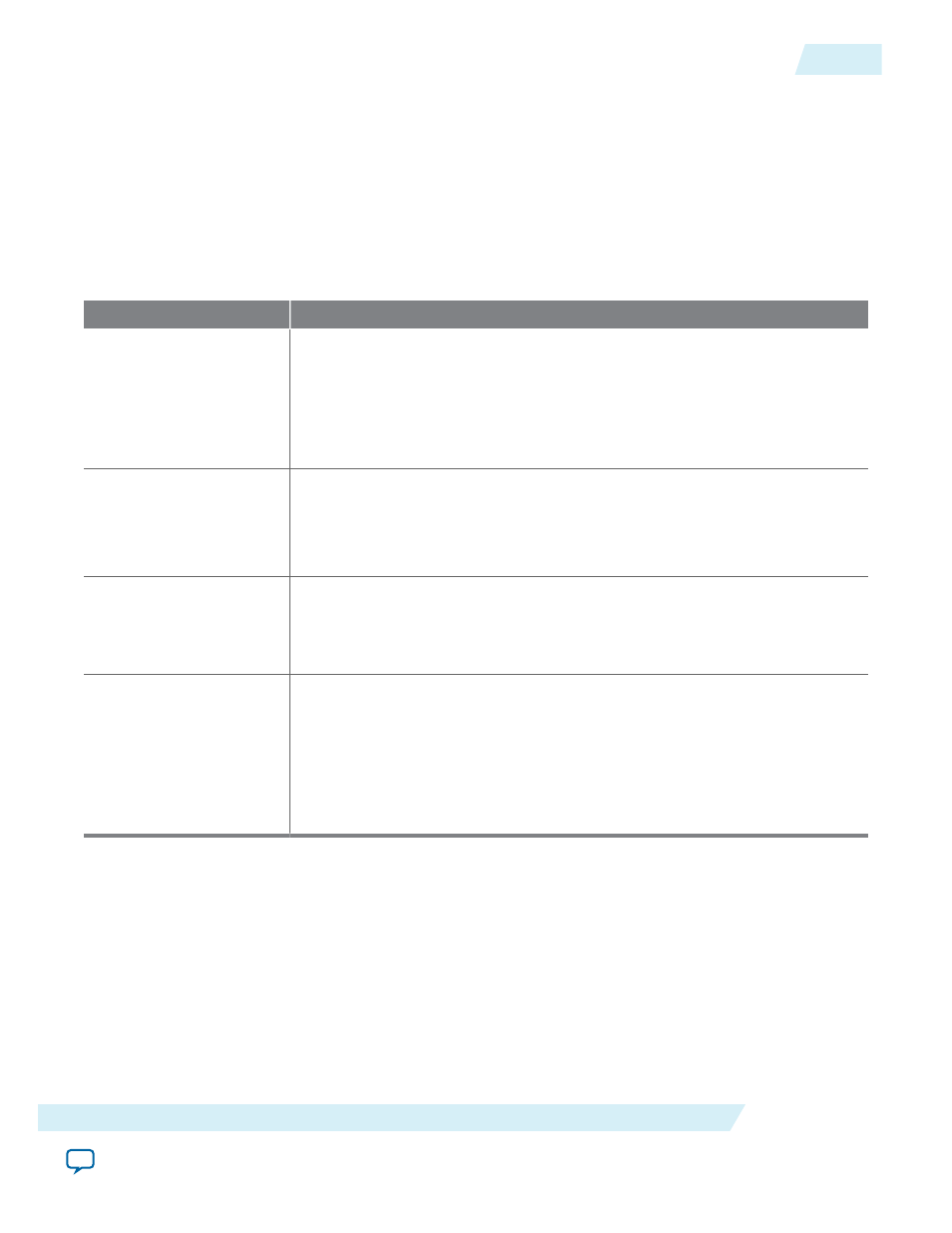

This table lists the inputs and corresponding outputs obtained from the simulation.

Table 15-2: Summary of Input Values and Corresponding Outputs

Time

Event

0 ns, start-up

dataa[]

value: C080 0000h

datab[]

value: 4000 0000h

Output value: All values seen on the output port before the 5th clock cycle are

merely due to the behavior of the system during start-up and should be

disregarded.

22.5 ns

Output value: 4100 0000h

The multiplication of a negative number with a positive number results in a

negative number. The absolute value of the result is reflected on the

result[]

port.

20 ns

dataa[]

value: 579D F479h

datab[]

value: 7F80 0000h

The value of

dataa[]

is normal while the value of

datab[]

is infinity.

42.5 ns

Output value: 7F80 0000h

Exception handling ports:

overflow

asserts

The multiplication of a normal value with infinity results in infinity and sets

the

overflow

port in the multiplier. The absolute value of the output is infinity

and the

overflow

port is also set as this assertion of the port is being carried

through from the corresponding

overflow

port in the multiplier.

ALTFP_ABS Signals

UG-01058

2014.12.19

ALTFP_ABS Signals

15-3

ALTFP_ABS IP Core

Altera Corporation