Altera_fp_matrix_inv signals, Altera_fp_matrix_inv signals -10, Altera_fp_matrix_inv – Altera Floating-Point User Manual

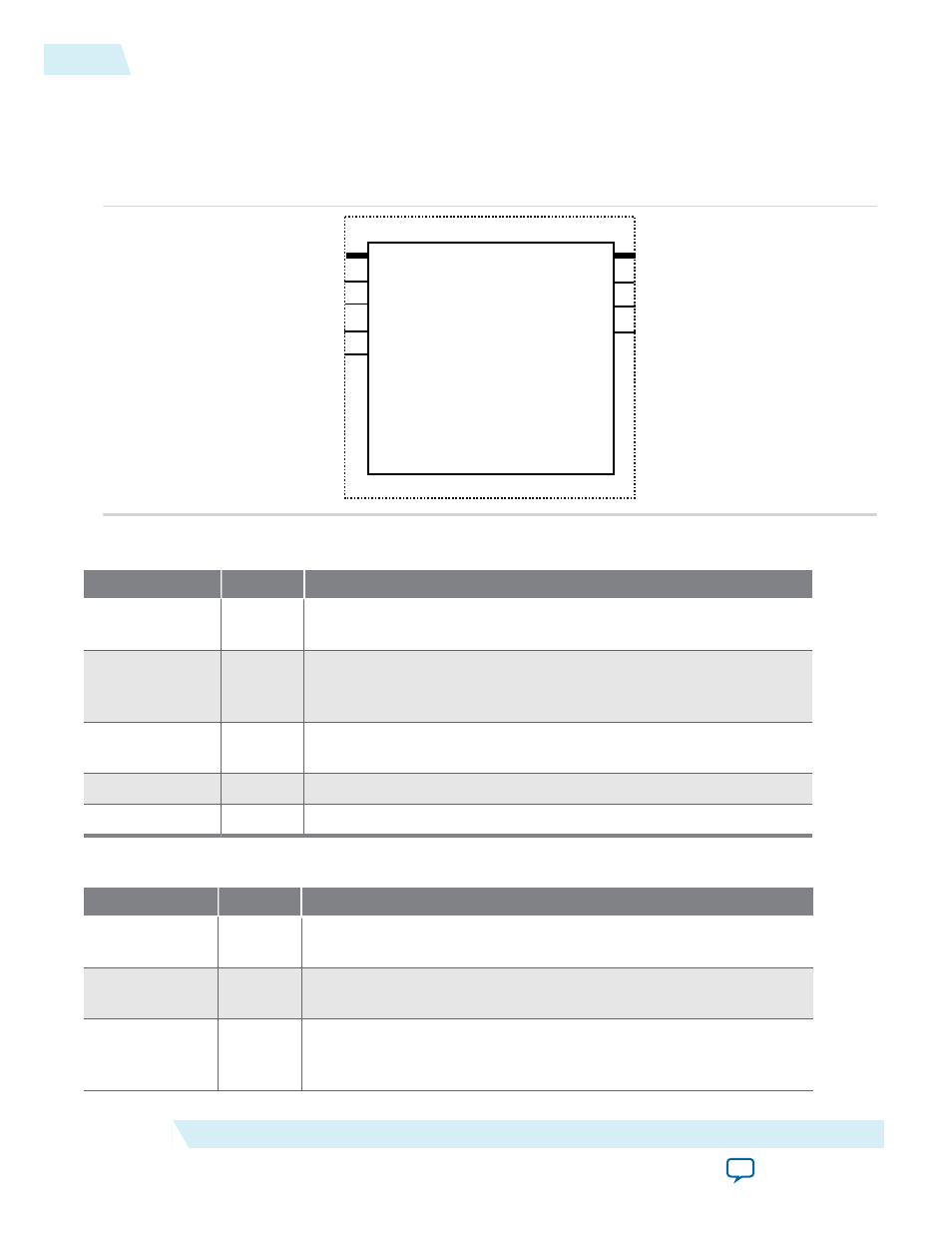

Page 34: Datain sysclk reset inst, Dataout[] busy outvalid done load enable

ALTERA_FP_MATRIX_INV Signals

Figure 2-5: ALTERA_FP_MATRIX_INV Signals

datain

sysclk

reset

inst

ALTERA_FP_MATRIX_INV

dataout[]

busy

outvalid

done

load

enable

Table 2-4: ALTERA_FP_MATRIX_INV Input Signals

Port Name

Required

Description

sysclk

Yes

The clock input to the ALTERA_FP_MATRIX_INV IP core. This is

the main system clock. All operations occur on the rising edge.

enable

No

Optional port. Allow calculation to take place when asserted. When

deasserted, no operation will take place and the outputs are

unchanged.

reset

No

Optional port. The core resets asynchronously when the

reset

signal

is asserted.

load

Yes

When asserted, loads the

LOADDATA

bus into the memory.

loaddata

Yes

Single-precision 32-bit matrix input value. Matrices load row by row.

Table 2-5: ALTERA_FP_MATRIX_INV Output Signals

Port Name

Required

Description

ready

Yes

When asserted, the core preprocesses the input data. The calculate

signal cannot be asserted until the

ready

signal is low.

outdata

Yes

Single-precision 32-bit matrix result value. The matrix result value is

written out row by row.

outvalid

Yes

When asserted, a valid output data is available. An entire row of the

result matrix is written out as a burst. There is a gap between row

outputs, which will depend on the parameters.

2-10

ALTERA_FP_MATRIX_INV Signals

UG-01058

2014.12.19

Altera Corporation

ALTERA_FP_MATRIX_INV IP Core