Altera Floating-Point User Manual

Page 130

1. In the ALTERA_FP_FUNCTIONS parameter editor, click the Basic tab.

2. Under the Performance category, in the Goal option, select Combined.

3. In the Target field, set your desired frequency (MHz).

4. In the Target field, set your desired latency (cycles).

5. Then, click Finish.

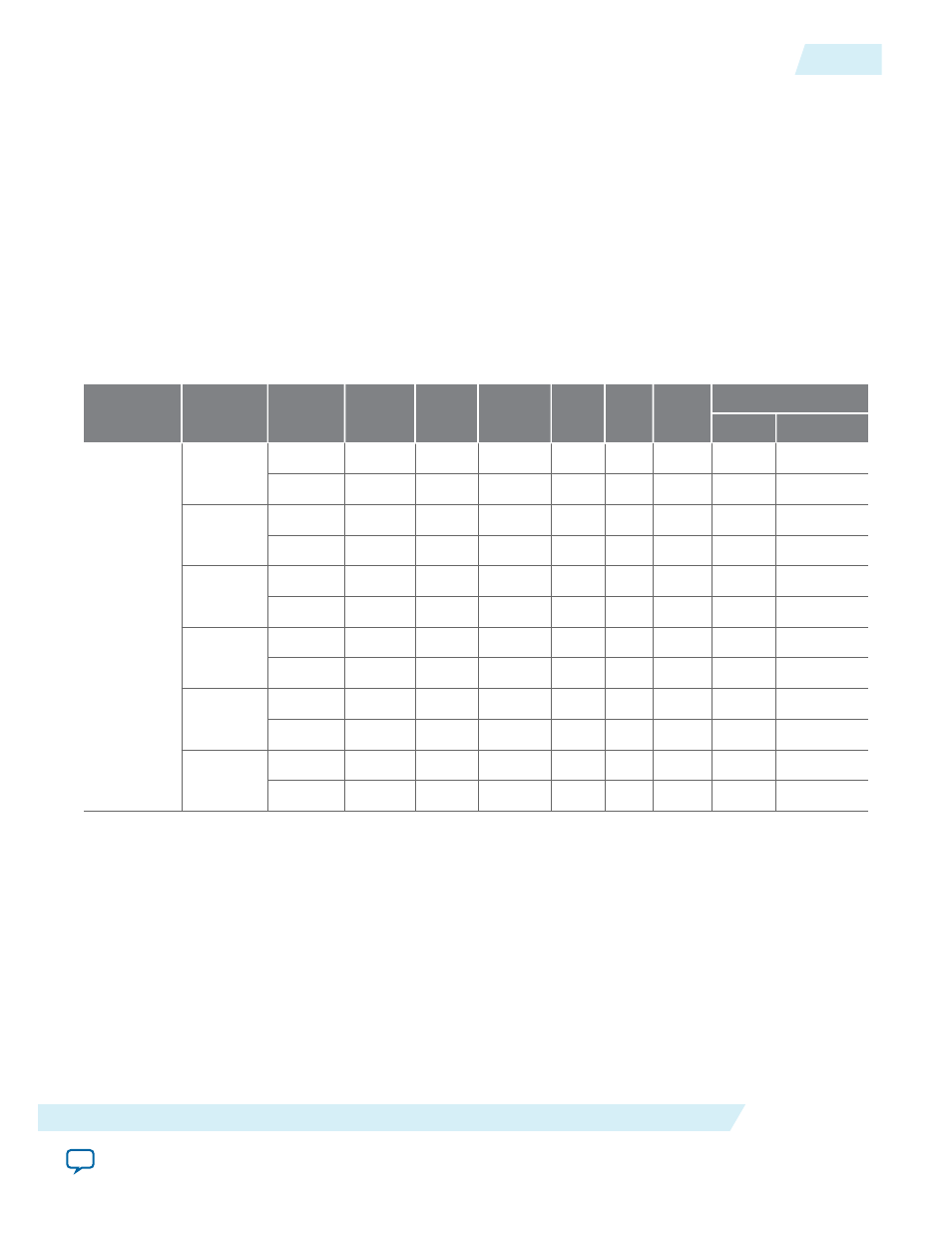

ALTERA_FP_FUNCTIONS Resource Utilization and Performance

These tables list the resource utilization and performance information for the

ALTERA_FP_FUNCTIONS IP core. The information was derived using the Quartus II software version

14.1. The frequency target was set to 200 MHz.

Table 18-2: Arithmetic

Family

Function

Precision Latency

f

MAX

ALMs

M10K M20

K

DSP

Blocks

Logic Registers

Primary Secondary

Arria V

(5AGXFB3H

4F40C5)

Abs

Single

0

—

33

0

—

0

0

0

Double

0

—

65

0

—

0

0

0

Add

Single

9

233.1

360

0

—

0

507

29

Double

12

251.95

886

0

—

0

1064

61

AddSubtra

ct

Single

9

249.31

477

0

0

0

651

63

Double

12

252.46

1161

0

0

0

1713

91

Cube Root

Single

9

275.18

132

6

—

2

132

20

Double

24

185.77

634

17

—

10

1297

58

Divide

Single

18

249

456

5

—

4

771

100

Double

35

185.29

1409

39

—

15

3035

138

Exp base

10

Single

16

212.72

547

3

—

2

675

18

Double

31

185.77

2194

0

—

10

2626

56

UG-01058

2014.12.19

ALTERA_FP_FUNCTIONS Resource Utilization and Performance

18-3

ALTERA_FP_FUNCTIONS IP Core

Altera Corporation