Altera Floating-Point User Manual

Page 112

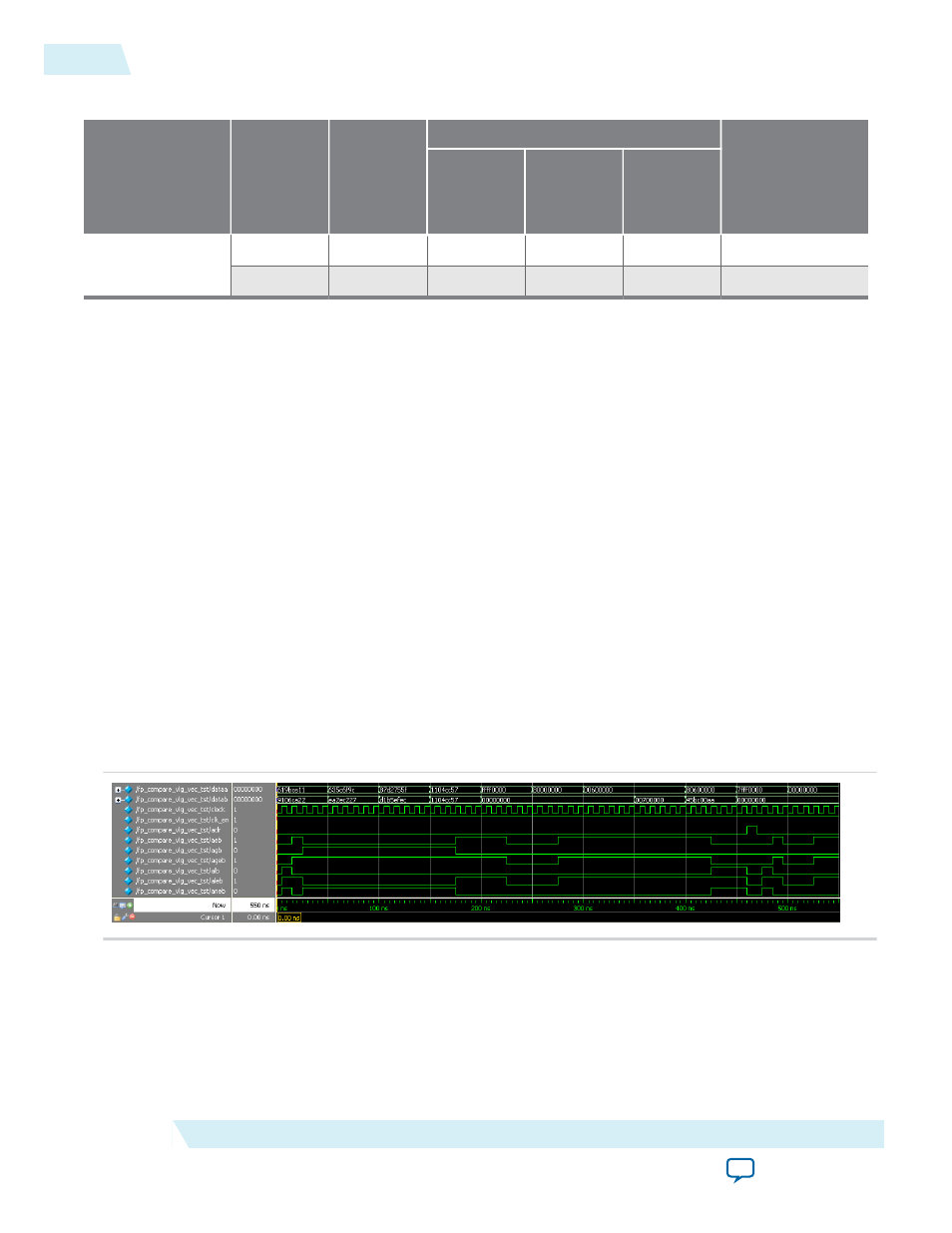

Table 16-1: ALTFP_COMPARE Resource Utilization and Performance for Stratix IV Devices

Device Family

Precision

Output

Latency

Logic Usage

f

MAX

(MHz)

Adaptive

Look-Up

Tables

(ALUTs)

Dedicated

Logic

Registers

(DLRs)

Adaptive

Look-Up

Modules

(ALMs)

Stratix IV

single

3

68

33

47

794

double

3

121

47

87

680

ALTFP_COMPARE Design Example: Comparison of Single-Precision

Format Numbers

This design example uses the ALTFP_COMPARE IP core to implement the comparison of single-

precision format numbers using the parameter editor in the Quartus II software.

Related Information

•

Floating-Point IP Cores Design Example Files

on page 1-16

•

Provides the design example files for the Floating-Point IP cores

•

Provides information about installation, usage, and troubleshooting

ALTFP_COMPARE Design Example: Understanding the Simulation Results

The simulation waveform in this design example is not shown in its entirety. Run the design example files

in the ModelSim-Altera software to see the complete simulation waveforms.

This figure shows the expected simulation results in the ModelSim-Altera software.

Figure 16-1: ALTFP_COMPARE Simulation Waveform

This design example implements a floating-point comparator for single-precision numbers. Both optional

input ports (

clk_en

and

aclr

) and all seven output ports (

ageb

,

aeb

,

agb

,

aneb

,

alb

,

aleb

, and

unordered

) are enabled.

The chosen output latency is 3. Therefore, the comparison operation generates the output result 3 clock

cycles later.

16-2

ALTFP_COMPARE Design Example: Comparison of Single-Precision Format Numbers

UG-01058

2014.12.19

Altera Corporation

ALTFP_COMPARE IP Core