Altfp_compare signals, Altfp_compare signals -3, Altfp_compare – Altera Floating-Point User Manual

Page 113

This table lists the inputs and corresponding outputs obtained from the simulation in the waveform.

Table 16-2: Summary of Input Values and Corresponding Outputs

Time

Event

0 ns, start-up

dataa[]

value: 619B CE11h

datab[]

value: 9106 CA22h

Output value: An undefined value is seen on the

result[]

port, which is ignored. All

values seen on the output port before the 3rd clock cycle are merely due to the

behavior of the system during start-up and should be disregarded.

25 ns

Output ports:

ageb

,

aneb

, and

agb

assert

350 ns

dataa[]

value: 0060 0000h

datab[]

value: 0070 0000h

Both input values are denormal numbers.

375 ns

Output ports:

aeb

,

ageb

, and

aleb

assert

Denormal inputs are not supported and are forced to zero before comparison takes

place, which results in the

dataa[]

value being equal to

datab[]

.

460 ns

The

aclr

signal is set for 1 clock cycle.

495.5 ns

The comparisons of subsequent data inputs are performed 3 clock cycles after the

aclr

signal deasserts.

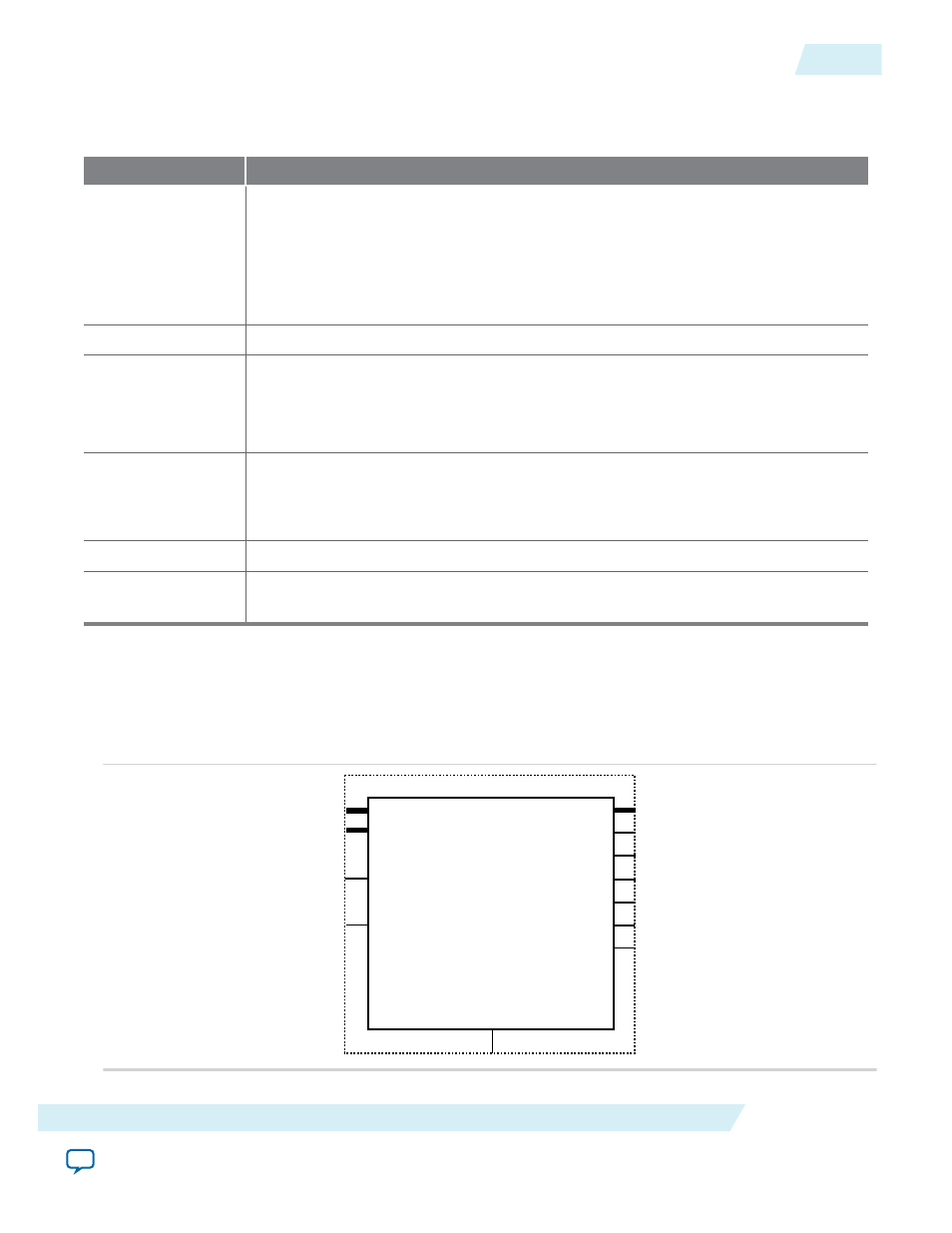

ALTFP_COMPARE Signals

Figure 16-2: ALTFP_COMPARE Signals

dataa[]

clk_en

clock

inst

ALTFP_COMPARE

aeb

aneb

agb

ageb

alb

unordered

aclr

datab[]

aleb

UG-01058

2014.12.19

ALTFP_COMPARE Signals

16-3

ALTFP_COMPARE IP Core

Altera Corporation