Altera Floating-Point User Manual

Page 58

Device family

Precision Optimiza‐

tion

Output

latency

Logic Usage

f

MAX

(MHz)

Adaptive

Look-Up

Tables

(ALUTs)

Dedicate

d Logic

Registers

(DLRs)

Adaptive

Logic

Modules

(ALMs)

18-bit

DSP

Low Latency Option

Stratix IV

Single

—

6

207

304

212

16

154

—

14

253

638

385

16

358

Double

—

10

714

1,077

779

44

151

—

24

765

2,488

1,397

44

238

ALTFP_DIV Design Example: Division of Single-Precision

This design example uses the ALTFP_DIV IP core to implement a floating-point divider for the division

of single-precision format numbers with low latency. This example uses the parameter editor to define the

core.

Related Information

•

Floating-Point IP Cores Design Example Files

on page 1-16

•

Provides the design example files for the Floating-Point IP cores

•

Provides information about installation, usage, and troubleshooting

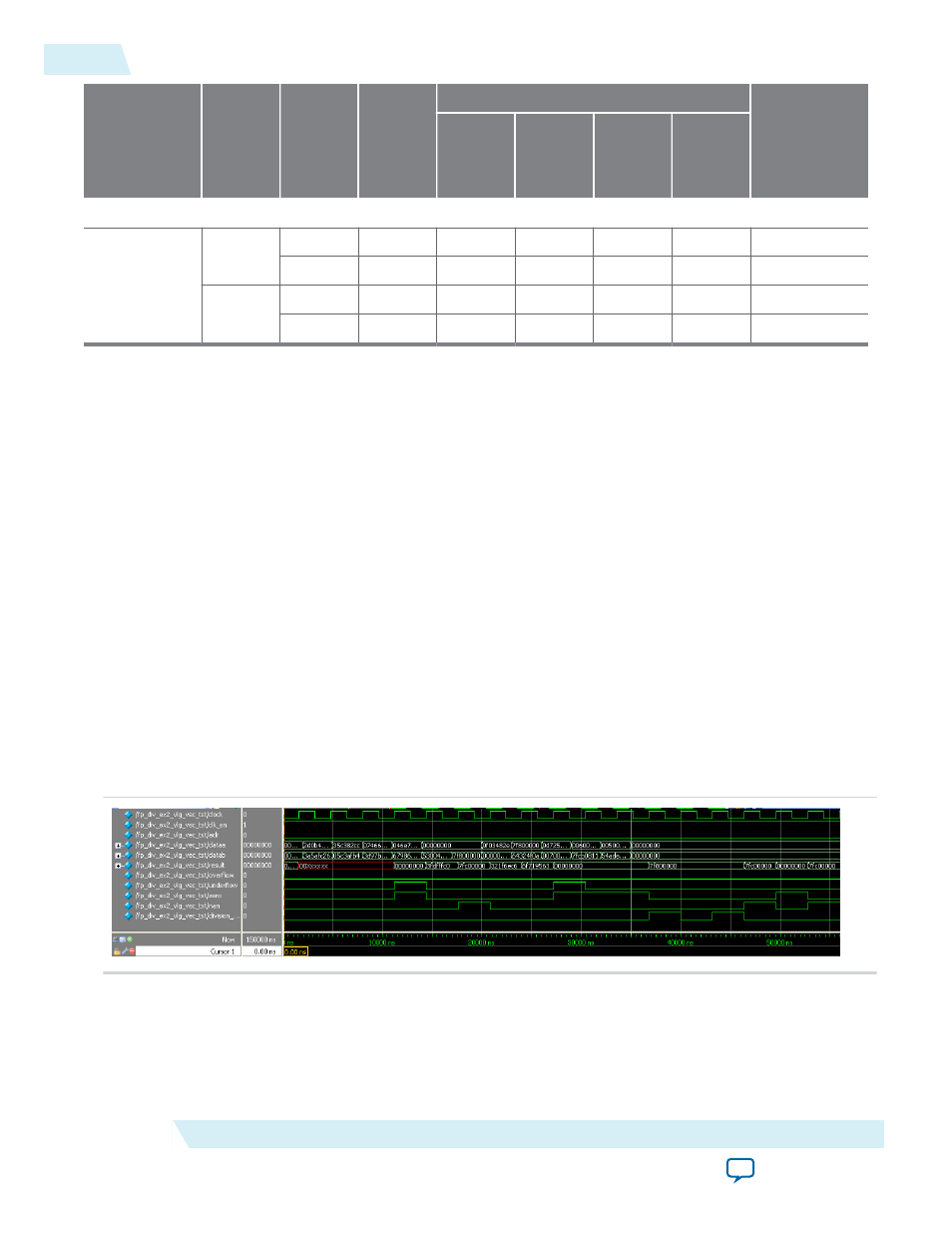

ALTFP_DIV Design Example: Understanding the Simulation Results

The simulation waveform in this design example is not shown in its entirety. Run the design example files

in the ModelSim-Altera software to see the complete simulation waveforms.

Figure 6-1: ALTFP_DIV Simulation Waveform

This figure shows the expected simulation results in the ModelSim-Altera software.

This design example implements a floating-point divider for the division of single-precision numbers

with a low latency option. The output latency is 6, hence every division generates the output result 6 clock

cycles later.

6-4

ALTFP_DIV Design Example: Division of Single-Precision

UG-01058

2014.12.19

Altera Corporation

ALTFP_DIV IP Core