Altera Floating-Point User Manual

Page 14

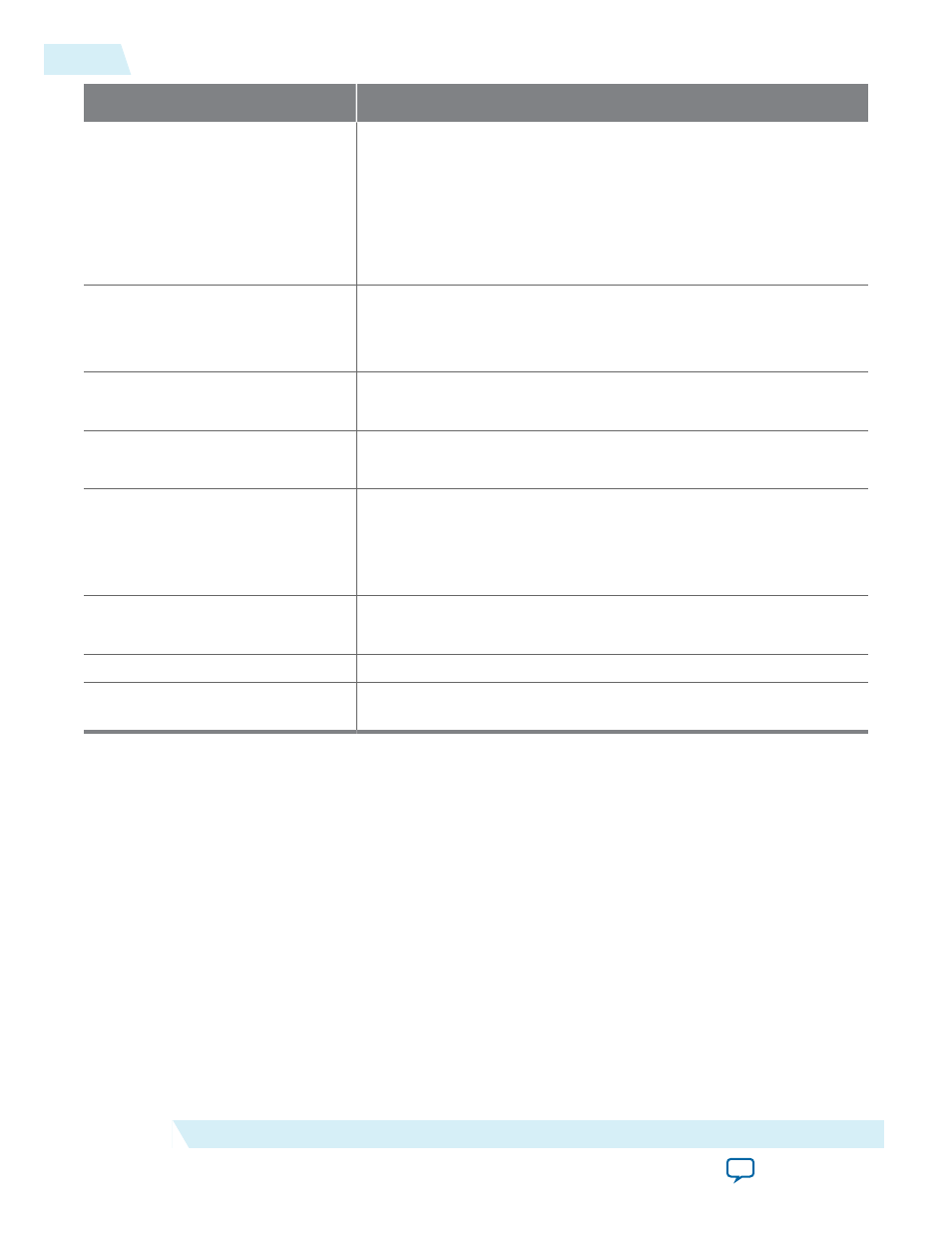

File Name

Description

<my_ip>.svd

Allows HPS System Debug tools to view the register maps of

peripherals connected to HPS within a Qsys system.

During synthesis, the .svd files for slave interfaces visible to System

Console masters are stored in the .sof file in the debug section.

System Console reads this section, which Qsys can query for register

map information. For system slaves, Qsys can access the registers by

name.

<my_ip>.v

or

<my_ip>.vhd

HDL files that instantiate each submodule or child IP core for

synthesis or simulation.

mentor/

Contains a ModelSim

®

script

msim_setup.tcl

to set up and run a

simulation.

aldec/

Contains a Riviera-PRO script

rivierapro_setup.tcl

to setup and run a

simulation.

/synopsys/vcs

/synopsys/vcsmx

Contains a shell script

vcs_setup.sh

to set up and run a VCS

®

simulation.

Contains a shell script

vcsmx_setup.sh

and

synopsys_ sim.setup

file to

set up and run a VCS MX

®

simulation.

/cadence

Contains a shell script

ncsim_setup.sh

and other setup files to set up

and run an NCSIM simulation.

/submodules

Contains HDL files for the IP core submodule.

<child IP cores>/

For each generated child IP core directory, Qsys generates

/synth

and

/

sim

sub-directories.

Specifying IP Core Parameters and Options (Legacy Parameter Editors)

Some IP cores use a legacy version of the parameter editor for configuration and generation. Use the

following steps to configure and generate an IP variation using a legacy parameter editor.

Note: The legacy parameter editor generates a different output file structure than the latest parameter

editor. Refer to Specifying IP Core Parameters and Options for configuration of IP cores that use the

latest parameter editor.

1-8

Specifying IP Core Parameters and Options (Legacy Parameter Editors)

UG-01058

2014.12.19

Altera Corporation

About Floating-Point IP Cores