8 interrupt acknowledge, Nterrupt, Cknowledge – Maxim Integrated Secure Microcontroller User Manual

Page 97: Interrupt priority control bits

Secure Microcontroller User’s Guide

97 of 187

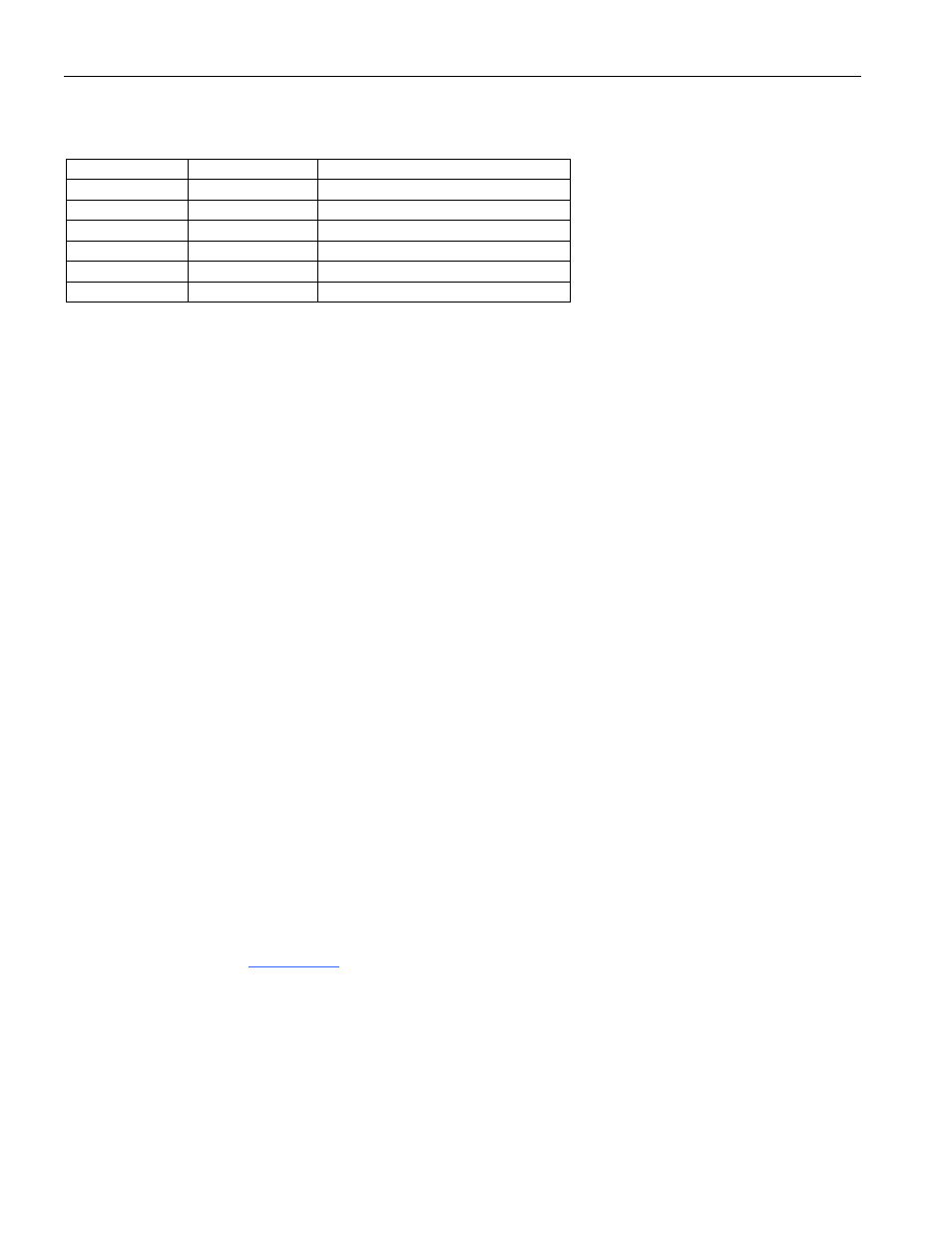

Each interrupt priority is determined by an individual bit as in the following table. Setting the appropriate

bit to a logic 1 will cause that interrupt to be high priority.

PRIORITY

FLAG

INTERRUPT SOURCE

1

PFW

Power-Fail Warning

2

IE0

External Interrupt 0

3

TF0

Timer 0 Interrupt

4

IE1

External Interrupt 1

5

TF1

Timer 1 Interrupt

6

RI+TI

Serial I/O Interrupt

Interrupt Priority Control Bits

All bits are read/write at any time and are cleared to 0 following any hardware reset.

IP.4

PS

Serial Port Priority

Programs Serial Port interrupts for high priority when set to 1. Low priority is

selected when cleared to 0.

IP.3

PT1

Timer 1 Priority

Programs Timer 1 interrupt for high priority when set to 1. Low priority is selected

when cleared to 0.

IP.2

PX1

External Interrupt 1 Priority

Programs External Interrupt 1 for high priority when set to 1. Low priority is

selected when cleared to 0.

IP.1

PT0

Timer 0 Priority

Program Timer 0 interrupt for high priority when set to 1. Low priority is selected

when cleared to 0.

IP.0

PX0

External Interrupt 0 Priority

Programs External Interrupt 0 for high priority when set to 1. Low priority is

selected when cleared to 0.

11.8 Interrupt Acknowledge

The various interrupt flags are sampled an latched once every machine cycle, specifically during clock

phase S5P2 (see CPU timing section) regardless of other interrupt related activity. Likewise, the latched

states of the flags are polled once every machine cycle for the sampling that took place during the

previous machine cycle.

A complete interrupt acknowledge sequence consists of a total of four machine cycles, labeled as IA1,

IA2, IA3, and IA4 in

. The various interrupt flags are sampled and latched once every

machine cycle, specifically during clock phase S5P2. This is shown in the diagram as IA1. If one or more

pending interrupt registers are latched, then during the following machine cycle (IA2) priority is resolved

between one or more active interrupt requests.

Also during IA2, the hardware checks the state of the machine to insure that the following criteria are met

before servicing the pending interrupt: