Figure 8-1. timed access, Table 8-a. timed-access-protected control bits, Table 8-a – Maxim Integrated Secure Microcontroller User Manual

Page 69: Figure 8-1

Secure Microcontroller User’s Guide

69 of 187

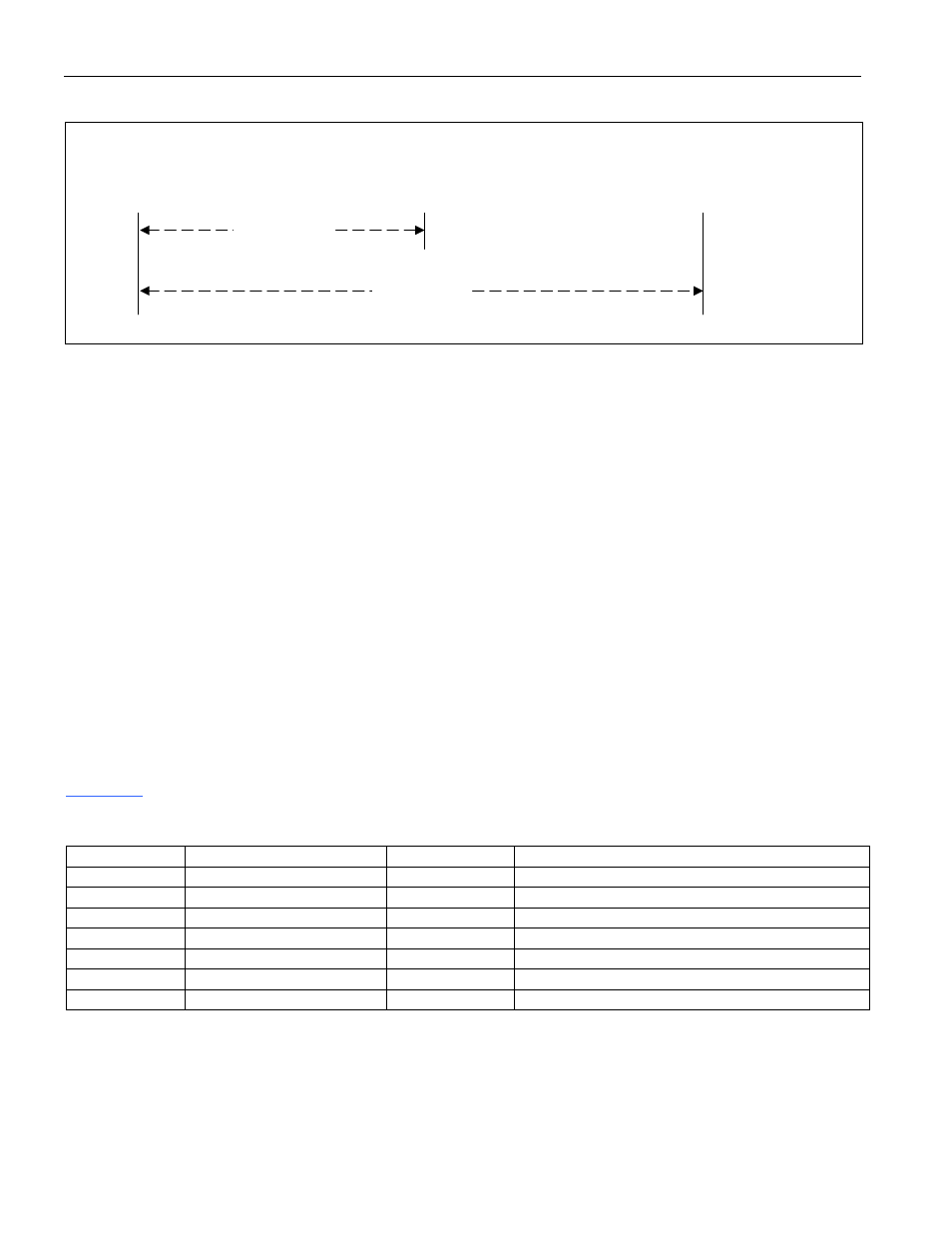

Figure 8-1. Timed Access

This code allows the reset of the watchdog timer:

MOV

0C7H,#0AAh

; 1st TA Value

MOV

0C7H,#055h

; 2nd TA Value

2 Cycles

SETB

IP.7

; Reset Watchdog Timer

1 Cycle

The watchdog timer bit may have been set using ORL IP, #80H, which takes 2 cycles.

This code allows the reset of the watchdog timer using a different approach:

MOV

A, #55h

; Setup Acc for fast write

MOV

0C7H, #0AAh

; 1st TA Value

MOV

0C7H, A

; 2nd TA Value

1 Cycle

MOV

A, IP

; Get Current IP

1 Cycle

ORL

A, #80H

; Prepare for fast write 1 Cycle

MOV

IP, A

; Reset Watchdog Timer

1 Cycle

Note that a new value for IP could have been retrieved from any direct register instead of

the current IP.

lists the bits that are write-access protected by the timed-access function.

Table 8-A. Timed-Access-Protected Control Bits

NAME

MICRO

LOCATION

DESCRIPTION

EWT

All Secure Micros

PCON.2

Enables the Watchdog Timer Reset function

RWT

All Secure Micros

IP.7

Resets the Watchdog Timer count

STOP

All Secure Micros

PCON.1

Stop Mode Enable

POR

All Secure Micros

PCON.6

Power-on Reset

PAA

DS5000 series

MCON.1

Partition Address Access bit (protects PA3–0)

PA3–0

DS5001, DS5002 series

MCON.7–4

Partition Address Bits

AE

DS5001, DS5002 series

RPCTL.4

Access Enable

The timed-access feature is especially useful in protecting the watchdog timer control bits during the

interval before the timeout of the watchdog timer. The EWT bit is protected to prevent errant software

from disabling the watchdog timer, and the protection of the RWT bit prevents an accidental restart of the

watchdog timeout. Thus software must really intend to reset the timeout in order to do so.

4 CYCLES

2 CYCLES

WRITE

AAh

WRITE

55h

WINDOW FOR

TIMED ACCESS CLOSES