4 expanded data memory timing, Xpanded, Emory – Maxim Integrated Secure Microcontroller User Manual

Page 135: Iming, Figure 15-6. expanded data memory write

Secure Microcontroller User’s Guide

135 of 187

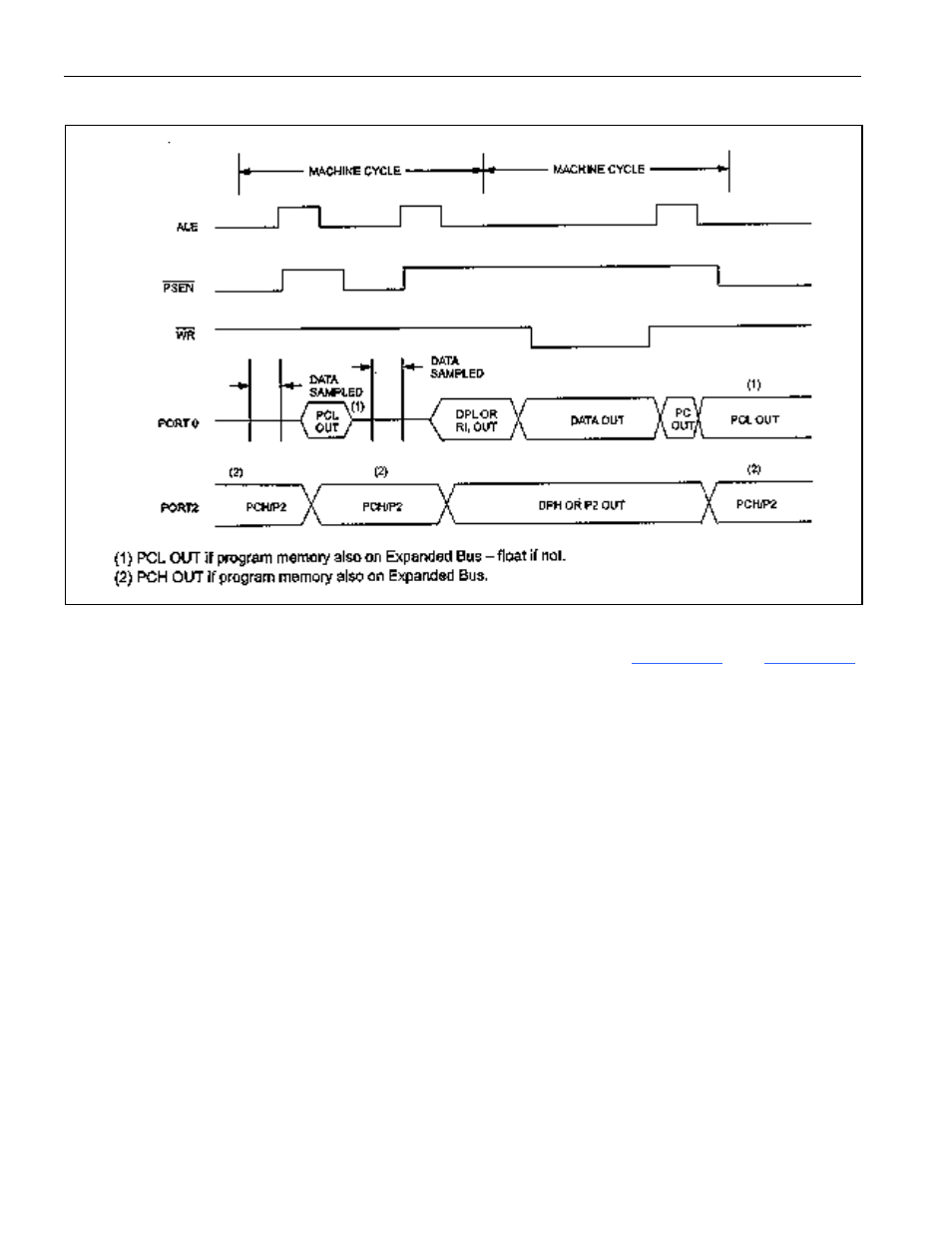

Figure 15-6. Expanded Data Memory Write

15.4 Expanded Data Memory Timing

The timing for the expanded data memory access cycle is illustrated in

and

Accesses to data memory on the expanded bus will occur any time that a MOVX instruction is executed

that references a data memory location that is mapped outside the area that has been assigned to the

expanded bus via the partition and range.

When a MOVX instruction is used with the data pointer register (e.g., MOVX @DPTR) to access a data

memory location on the expanded bus, a full 16-bit address will be generated to the external memory. The

16-bit address is generated on P2 and P0 that are the same pins as for a program memory fetch from

expanded memory. The contents of the SFR latch for Port 2 will not be modified, however, during the

execution of a data memory fetch cycle on the expanded bus. If the MOVX instruction is not followed by

another instruction requiring a cycle on the expanded bus, then the original contents of the Port 2 SFR

latch will appear once again during the next machine cycle.

Multiplexed address/data information is output on Port 0 during the execution of a data memory cycle on

the expanded bus. The falling edge of ALE can be used to latch the lower eight bits of address

information into an external transparent latch (e.g., 74LS373 or equivalent). During the second cycle of a

MOVX instruction, the first ALE pulse will not be generated so that valid address information will

remain in the latch and be presented to the external memory device for the duration of the cycle. Port 0 is

written with all 1s (0FFH) so that the original information contained in this register is lost. Also, Port 0

pins are driven with internal buffers when 1s are output during expanded data memory cycles.