11 program status flags, Rogram, Tatus – Maxim Integrated Secure Microcontroller User Manual

Page 50: Lags

Secure Microcontroller User’s Guide

50 of 187

highest order 5 bits for the next contiguous instruction (PC + 2) and concatenating them with the lowest

order 11-bit field contained in the current instruction. The 11-bit field provides an efficient instruction

encoding of a destination address for these instructions.

ACALL 100H

; Call to the subroutine at address

; 0100H + current page address

If the instruction were located at 0830h, the destination address would be 800H + 100H or 900H.

Extended Addressing

Extended addressing is used in the control transfer instructions to specify a 16-bit destination address

within the entire 64kB addressable range of the secure microcontroller.

LJMP 0FF80H

; Jump to address 0FF80H

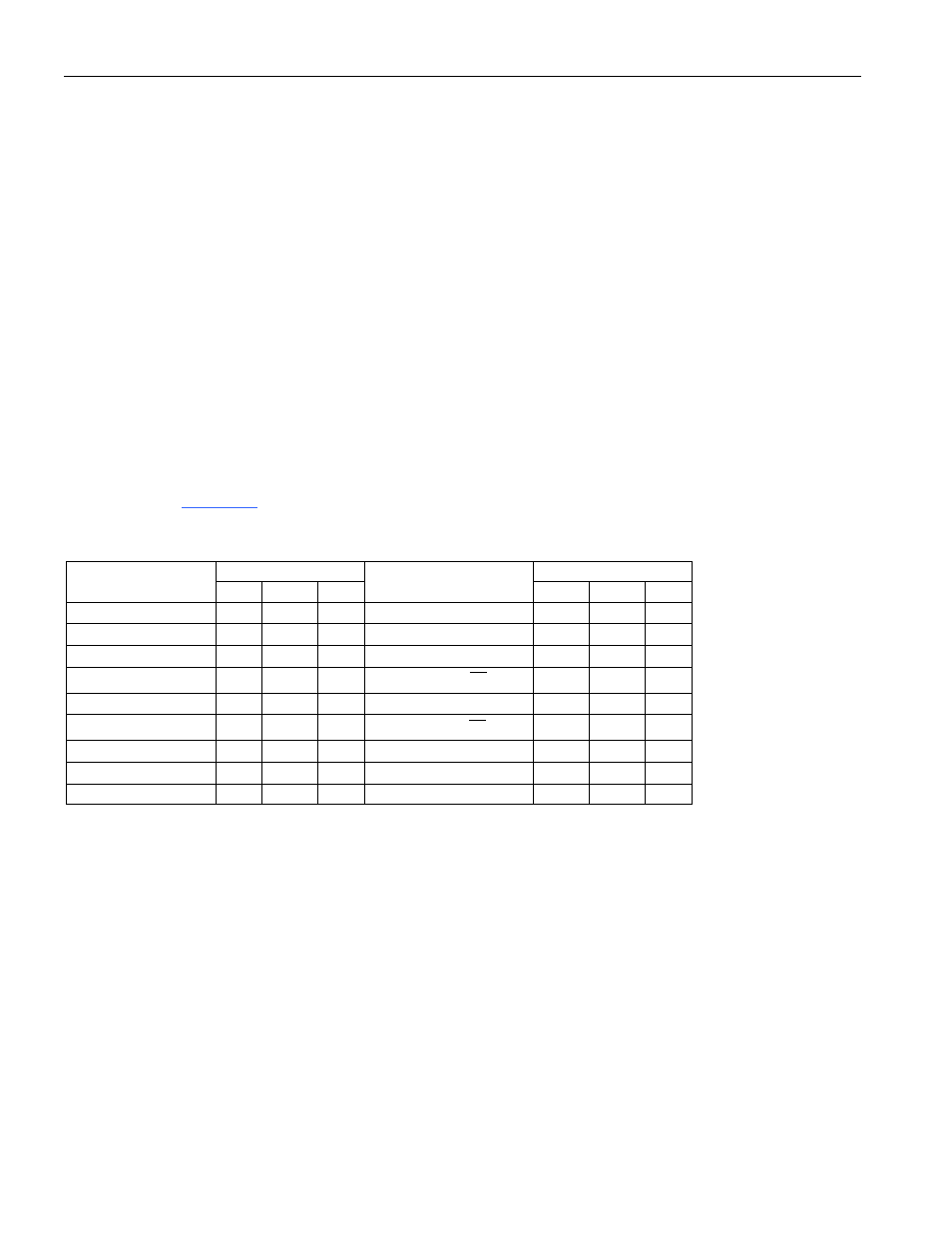

4.11 Program Status Flags

The PSW register contains the program status flags. Instructions that affect the states of the flags are

summarized in

Table 4-A. Instructions That Affect Program Status Flag

INSTRUCTION

FLAGS

INSTRUCTION

FLAGS

C

OV

AC

C

OV

AC

ADD

±

±

±

CLR C

0

ADDC

±

±

±

CPL C

±

SUBB

±

±

±

ANL C, bit

±

MUL

0

±

ANL C,

bit

±

DIV

0

±

ORL C, bit

±

DA

±

ORL C,

bit

±

RRC

±

MOV C, bit

±

RLC

±

CJNE

±

SETB C

1

0 = Cleared to 0

1 = Set to a 1

± = Modified according to the result of the operation.