Timer control register tcon, 088h – Maxim Integrated Secure Microcontroller User Manual

Page 37

Secure Microcontroller User’s Guide

37 of 187

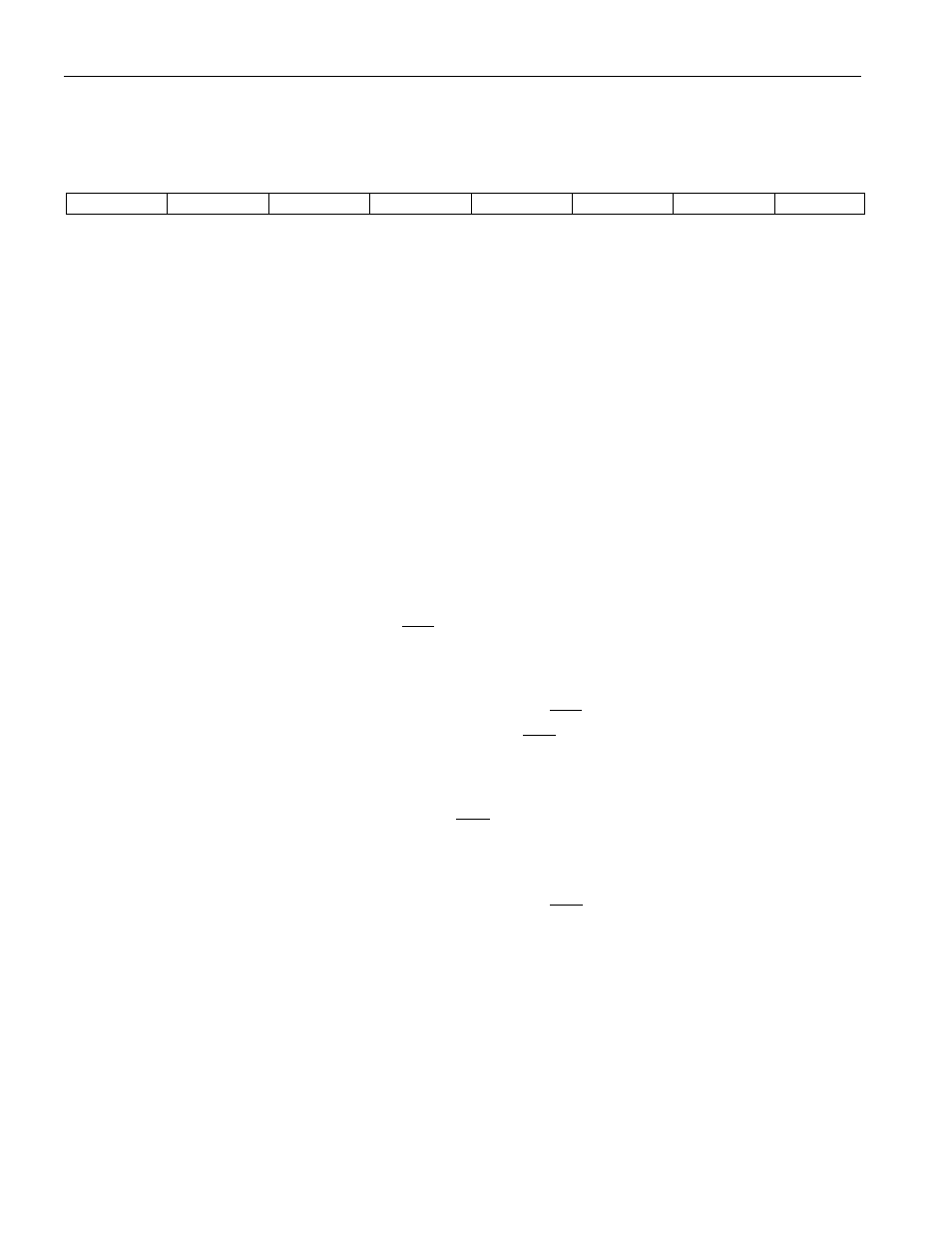

Timer Control Register

TCON, 088H

D7

D6

D5

D4

D3

D2

D1

D0

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

R = Unrestricted Read Access, W = Unrestricted Write Access, T = Timed-access Write Only, n = Value after Reset, * = Special: see description

TCON.7

TF1

Timer 1 Overflow Flag

Status bit set to 1 when timer 1 overflows from a previous count value of all 1s.

Cleared to 0 when CPU vectors to timer 1 interrupt service routine.

TCON.6

TR1

Timer 1 Run Control

When set to 1 by software, timer 1 operation is enabled. Timer 1 is disabled when

cleared to 0.

TCON.5:

TF0

Timer 0 Overflow

Status bit set to 1 when timer 0 overflows from a previous count value of all 1s.

Cleared to 0 when CPU vectors to timer 0 interrupt service routine.

TCON.4:

TR0

Timer 0 Run Control

When set to 1 by software, timer 0 operation is enabled. Timer 0 is disabled when

cleared to 0.

TCON.3:

IE1

Interrupt 1 Edge Detect

Set to 1 to signal when a 1-to-0 transition (IT = 1) or a low level (IT = 0) has been

detected on the

INT1

pin. Cleared to 0 by hardware when interrupt processed only

if IT1 = 1.

TCON.2:

IT1

Interrupt 1 Type Select

When set to 1, 1-to-0 transitions on

INT1

are used to generate interrupt requests

from this pin. When cleared to 0,

INT1

is level activated.

TCON.1:

IE0

Interrupt 0 Edge Detect

Set to 1 to signal when a 1-to-0 transition (IT0 = 1) or a low level (IT0 = 0) has

been detected on the

INT0

pin. Cleared to a 0 by hardware when interrupt

processed only if IT0 = 1.

TCON.0:

IT0

Interrupt 0 Type Select

When set to 1, 1-to-0 transitions on

INT0

are used to generate interrupt requests

from this pin. When cleared to 0, INT0 is level activated.