Interrupt enable register ie, 0a8h – Maxim Integrated Secure Microcontroller User Manual

Page 40

Secure Microcontroller User’s Guide

40 of 187

Interrupt Enable Register

IE, 0A8H

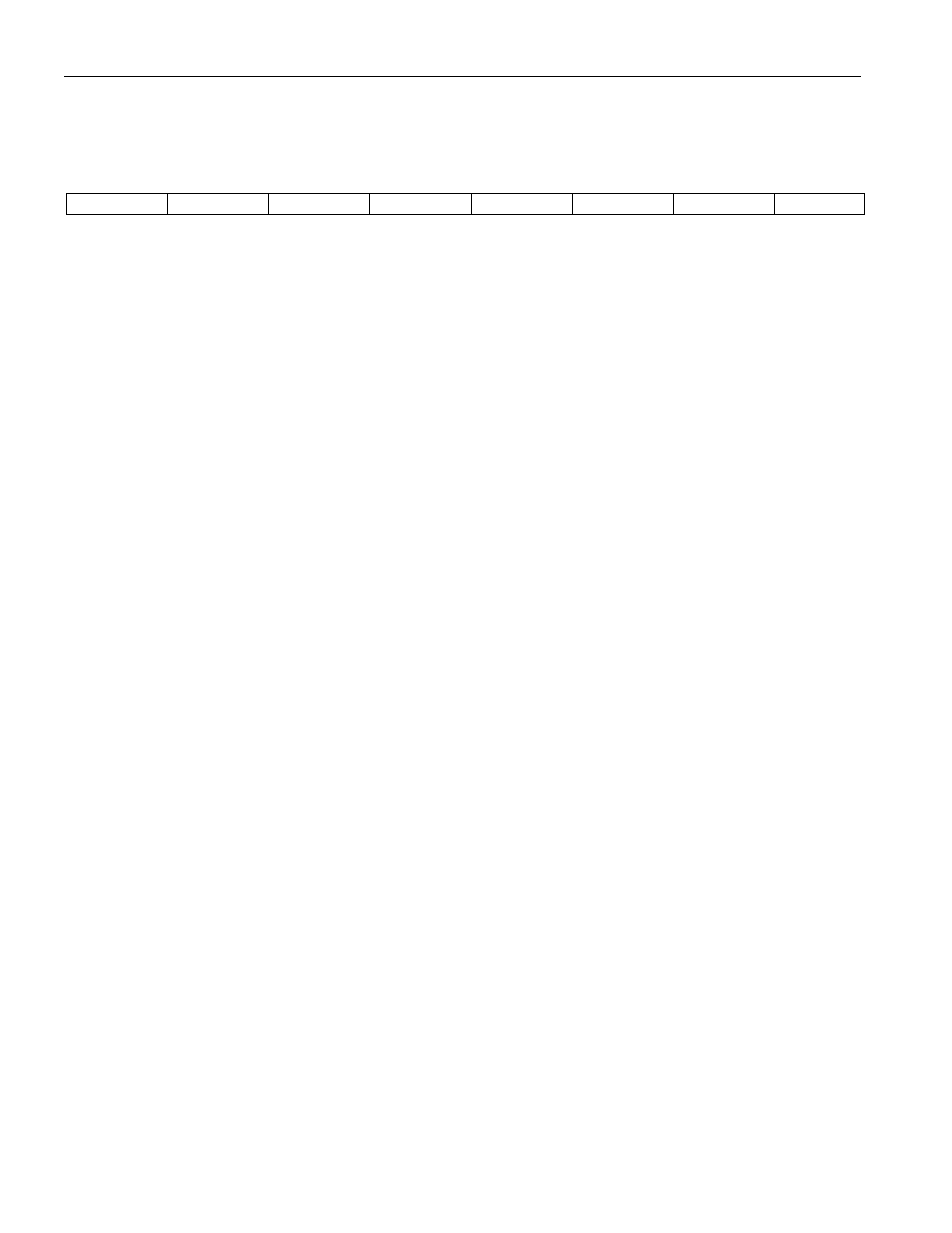

D7

D6

D5

D4

D3

D2

D1

D0

EA

—

—

ES

ET1

EX1

ET0

EX0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

R = Unrestricted Read Access, W = Unrestricted Write Access, T = Timed-access Write Only, n = Value after Reset, * = Special: see description

IE.7

EA

Global Interrupt Enable

When set to 1, each interrupt except for PFW may be individually enabled or

disabled by setting or clearing the associated IEx bit. When cleared to 0,

interrupts are globally disabled and no pending interrupt request will be

acknowledged except for PFW.

IE.4

ES

Enable Serial Interrupt

When set to 1, an interrupt request from either the serial port’s TI or RI flags

can be acknowledged. Serial I/O interrupts are disabled when cleared to 0.

IE.3

ET1

Enable Timer 1 Interrupt

When set to 1, an interrupt request from Timer 1’s TF1 flag can be

acknowledged. Timer interrupts are disabled when cleared to 0.

IE.2

EX1

Enable External Interrupt 1

When set to 1, an interrupt request from the IE1 flag can be acknowledged.

Interrupts are disabled from this source when cleared to 0.

IE.1

ET0

Enable Timer 0 Interrupt

When set to 1, an interrupt request from timer 0’s TF0 flag can be

acknowledged. Interrupts are disabled from this source when cleared to 0.

IE.0

EX0

Enable External Interrupt 0

When set to 1, an interrupt from the IE0 flag can be acknowledged. Interrupts

are disabled from this source when cleared to 0.