Power control register pcon, 087h – Maxim Integrated Secure Microcontroller User Manual

Page 36

Secure Microcontroller User’s Guide

36 of 187

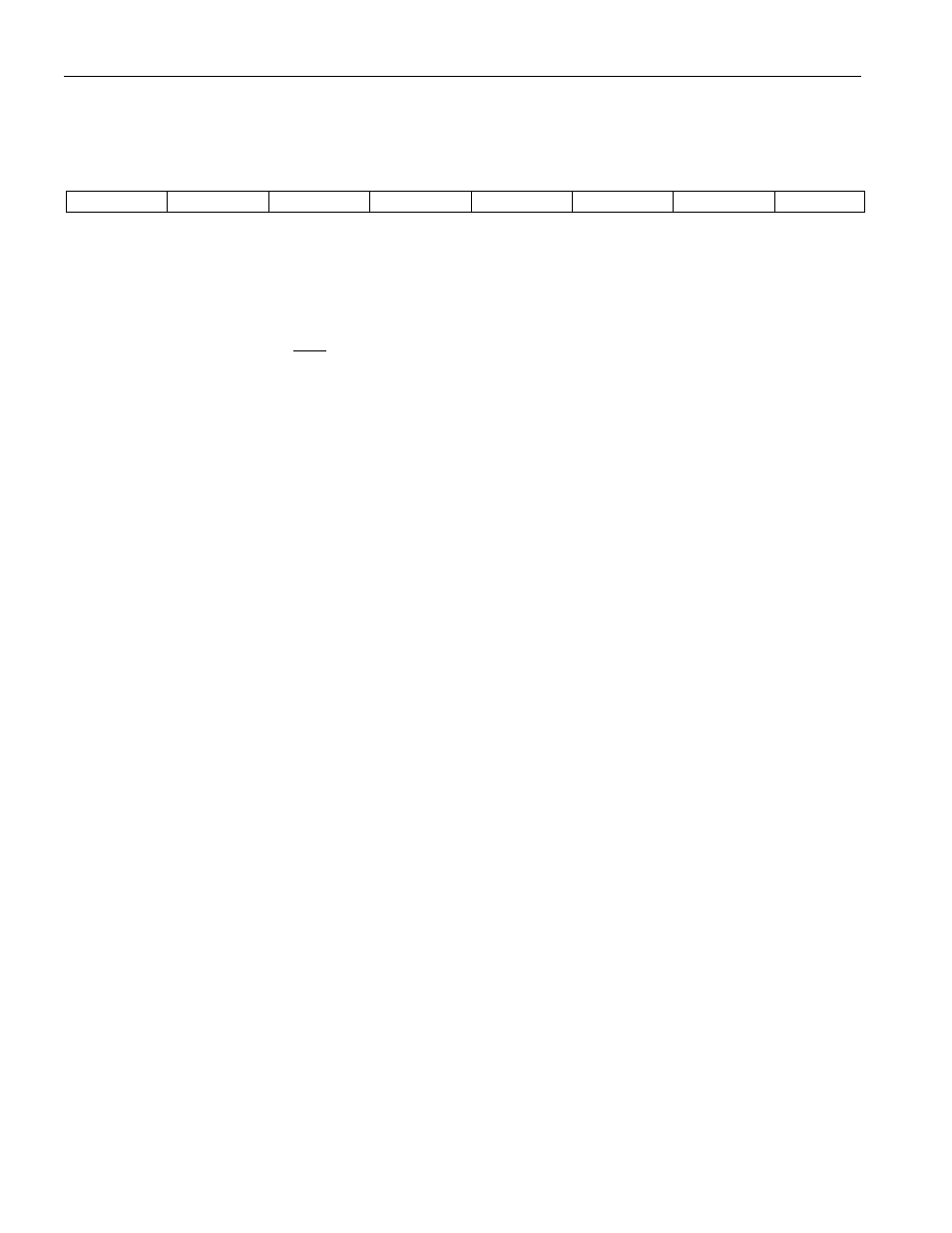

Power Control Register

PCON, 087H

D7

D6

D5

D4

D3

D2

D1

D0

SMOD

POR

PFW

WTR

EPFW

EWT

STOP

IDL

RW-0

RT-*

R-*

R-*

RW-0

RT-*

RT-0

RW-0

R = Unrestricted Read Access, W = Unrestricted Write Access, T = Timed-access Write Only, n = Value after Reset, * = Special: see description

PCON.7

SMOD

Double Baud Rate

When set to 1, the baud rate is doubled when the serial port is being used in modes

1, 2, or 3.

PCON.6

POR

Power-On Reset

Indicates that the previous reset was initiated during a power-on sequence. This bit

is cleared to 0 when power-on reset occurs, and remains 0 until it is set to 1 by

software.

PCON.5

PFW

Power-Fail Warning

Indicates that a potential power failure is in progress. Set to 1 whenever V

CC

is

below the V

PFW

threshold. Cleared to 0 immediately following a read operation of

the PCON register. Once set, it remains set until the read operation occurs,

regardless of activity on V

CC

. After PFW is cleared by a read, it returns to 1 if V

CC

< V

PFW

. This bit is cleared to a 0 during a power-on reset.

PCON.4

WTR

Watchdog Timer Reset

Set to 1 following a watchdog timer timeout. If WTR is enabled, it indicates the

cause of the reset. Cleared to 0 immediately following a read of the PCON

register. This bit is set to 1 after a WTR and cleared to 0 on a power-on reset.

Remains unchanged during other types of resets.

PCON.3

EPFW

Enable Power-Fail Interrupt

Enables (EPFW = 1) or disables (EPFW = 0) the power-fail interrupt.

PCON.2

EWT

Enable Watchdog Timer

Enables (EWT = 1) or disables (EWT = 0) the WTR. This bit is cleared to 0 on a

no-V

LI

power-on reset and remains unchanged during other types of reset.

PCON.1

STOP

Stop

Used to invoke the stop mode. When set to 1, program execution terminates

immediately and stop mode operation commences. Cleared to 0 when program

execution resumes following a hardware reset.

PCON.0

IDL

Idle

Used to invoke the idle mode. When set to 1, program execution is halted and

resumes when the idle bit is cleared to 0 following an interrupt or a hardware reset.