5 ds5001/ds5002 memory-mapped peripherals, Ds5001/ds5002, Emory – Maxim Integrated Secure Microcontroller User Manual

Page 27: Apped, Eripherals

Secure Microcontroller User’s Guide

27 of 187

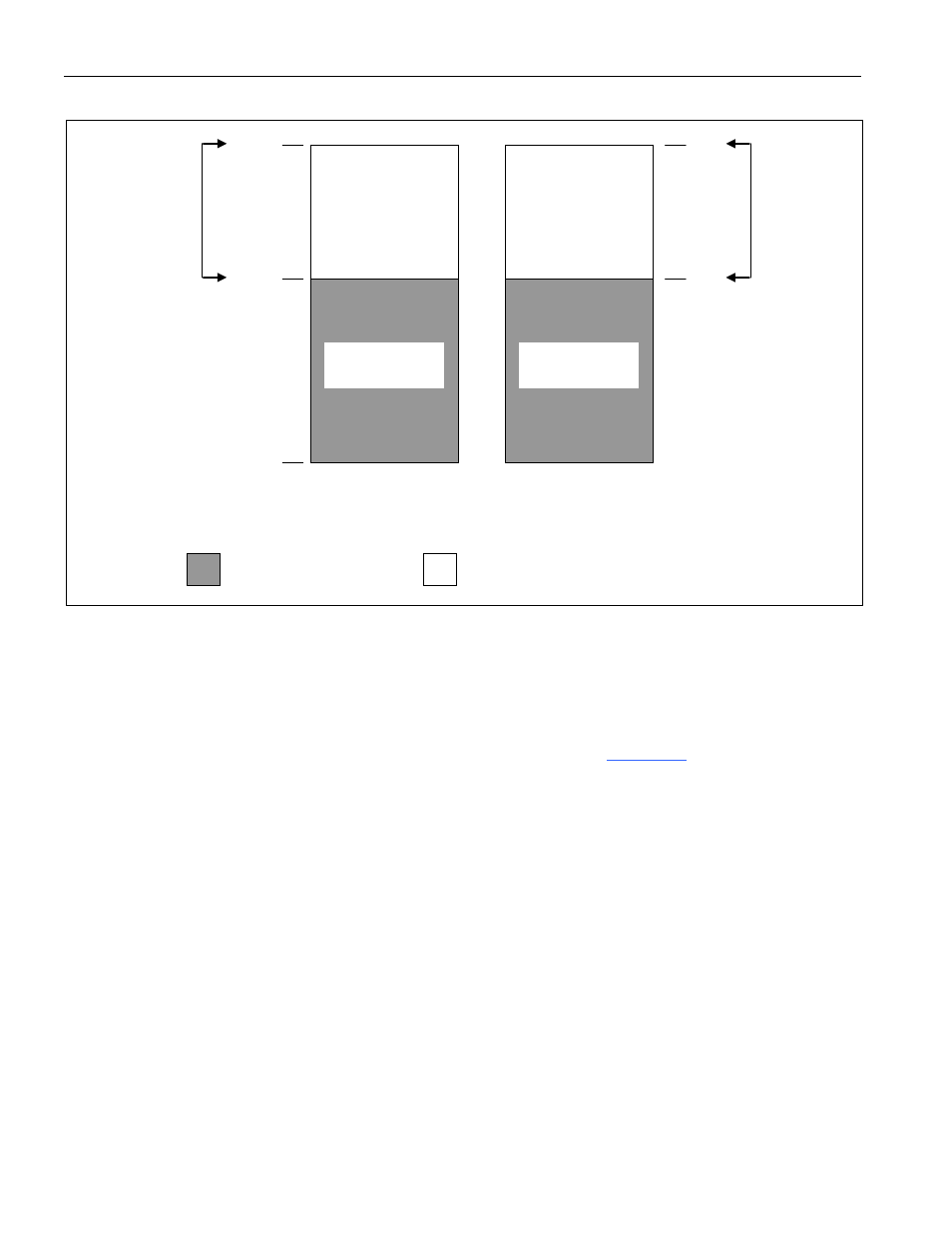

Figure 4-5. Nonpartitionable Memory Map for DS5001/DS5002 Series

4.5 DS5001/DS5002 Memory-Mapped Peripherals

The DS5001FP and DS5002FP provide four peripheral chip enables (

PE4–PE1) designed to access

unencrypted peripherals on the bytewide bus. While PES = 1, all MOVX-based instructions present

unencrypted address and data on the bytewide bus. During these instructions the device asserts peripheral

chip-enable signals instead of the standard chip-enable signals based on the logical address. The

peripheral chip enables are decoded on 16kB boundaries, as shown in

. The PES bit operates

the same way in both partitionable and nonpartitionable modes.

The peripheral enables interfaced to battery-backed and nonbattery-backed peripherals. The lowest two

peripheral enables,

PE1 and PE2, are battery backed by the DS5001/DS5002. This means that when V

CC

is removed, the device drives these chip enables to a logic high inactive state. These signals should be

interfaced to SRAM and other devices that are battery backed. The upper two peripheral enables,

PE3 and

PE4, are not battery backed by the DS5001/DS5002. This means that when V

CC

is removed, the device

allows these signals to float to an undefined state. These signals should be interfaced to ADCs, UARTs,

and any other peripheral that is powered by V

CC

rather than V

CCO

.

A novel use of the PES signals is to double the available MOVX memory space. When set, the PES bit in

essence creates an overlay of 64kB, using the same MOVX addresses. By toggling the PES bit on and off,

the device can access up to 128kB of MOVX memory.

On occasion, a memory-mapped peripheral is needed that interfaces directly to an 8051 multiplexed bus.

When this occurs, MOVX instructions can be forced to use the expanded bus in any mode with the EXBS

bit (RPCTL.5). Setting this bit to logic 1 forces all MOVX instructions to the expanded bus. While EXBS

BYTEWIDE

BUS ACCESS

BYTEWIDE

BUS ACCESS

FFFFh

7FFFh

0000

64kB

32kB

PROGRAM

MEMORY

DATA

MEMORY

PROGRAM

RANGE

DATA

RANGE

PES=0

= BYTEWIDE ACCESS

(NV RAM)

= EXPANDED BUS ACCESS ON PORTS 0 AND 2