3 ddi signal description: hdmi/dvi, 6 lvds, 1 signal description – IEI Integration ICE-DB-T6 User Manual

Page 57: Lvds, Table 3-13: ddi signal descriptions – hdmi/dvi

Type 6 Carrier Board Design Guide

Page 47

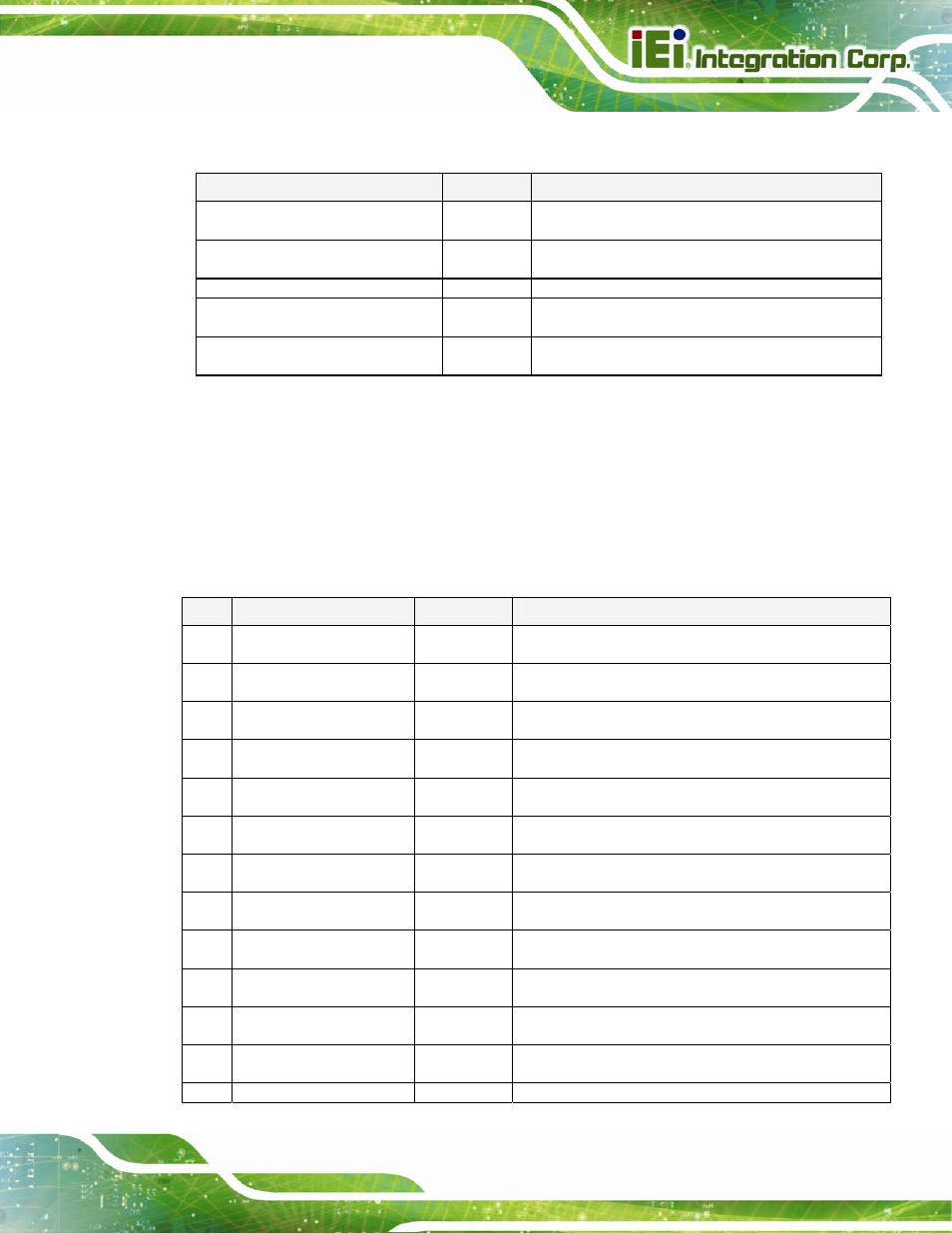

3.5.2.3 DDI Signal Description: HDMI/DVI

Signal

I/O

Description

TMDS[1:3]_DATA[0:2]+

TMDS[1:3]_DATA[0:2]-

O PCIe

HDMI/DVI TMDS lanes 0, 1 and 2 differential

pairs.

TMDS[1:3]_CLK+

TMDS[1:3]_CLK-

O PCIe

HDMI/DVI TMDS Clock differential pair.

HDMI[1:3]_HPD

I

HDMI/DVI hot-plug detect

HDMI[1:3]_CTRLCLK I/O

3.3V

CMOS

HDMI/DVI I2C control clock

HDMI[1:3]_CTRLDATA I/O

3.3V

CMOS

HDMI/DVI I2C control data

Table 3-13: DDI Signal Descriptions – HDMI/DVI

3.6 LVDS

3.6.1 Signal Description

Table 3-14 shows COM Express LVDS and LCD signals, including pin number, signals,

I/O and descriptions.

Pin

Signal

I/O

Description

A71

A72

LVDS_A0+

LVDS_A0-

O

LVDS channel A differential signal pair 0

A73

A74

LVDS_A1+

LVDS_A1-

O

LVDS channel A differential signal pair 1

A75

A76

LVDS_A2+

LVDS_A2-

O

LVDS channel A differential signal pair 2

A78

A79

LVDS_A3+

LVDS_A3-

O

LVDS channel A differential signal pair 3

A81

A82

LVDS_A_CK+

LVDS_A_CK-

O

LVDS channel A differential clock pair

B71

B72

LVDS_B0+

LVDS_B0-

O

LVDS channel B differential signal pair 0

B73

B74

LVDS_B1+

LVDS_B1-

O

LVDS channel B differential signal pair 1

B75

B76

LVDS_B2+

LVDS_B2-

O

LVDS channel B differential signal pair 2

B77

B78

LVDS_B3+

LVDS_B3-

O

LVDS channel B differential signal pair 3

B81

B82

LVDS_B_CK+

LVDS_B_CK-

O

LVDS channel B differential clock pair

A77 LVDS_VDD_EN

O 3.3V

CMOS

LVDS flat panel power enable.

B79 LVDS_BKLT_EN

O 3.3V

CMOS

LVDS flat panel backlight enable high active signal

B83 LVDS_BKLT_CTRL

O 3.3V

LVDS flat panel backlight brightness control