1 peg (pci express graphic), 1 signal description, Xpress – IEI Integration ICE-DB-T6 User Manual

Page 30: Raphic

Type 6 Carrier Board Design Guide

Page 20

3.1 PEG (PCI Express Graphic)

The PEG Port can utilize COM Express PCIe lanes 16 through 32 to drive a PCIe x16 link

for a PCI Express Graphics card. It supports a theoretical bandwidth of up to 4 GB/s. Each

lane of the PEG Port consists of a receiver and transmit differential signal pair. The

corresponding signals can be found on the Module connector rows C and D.

3.1.1 Signal Description

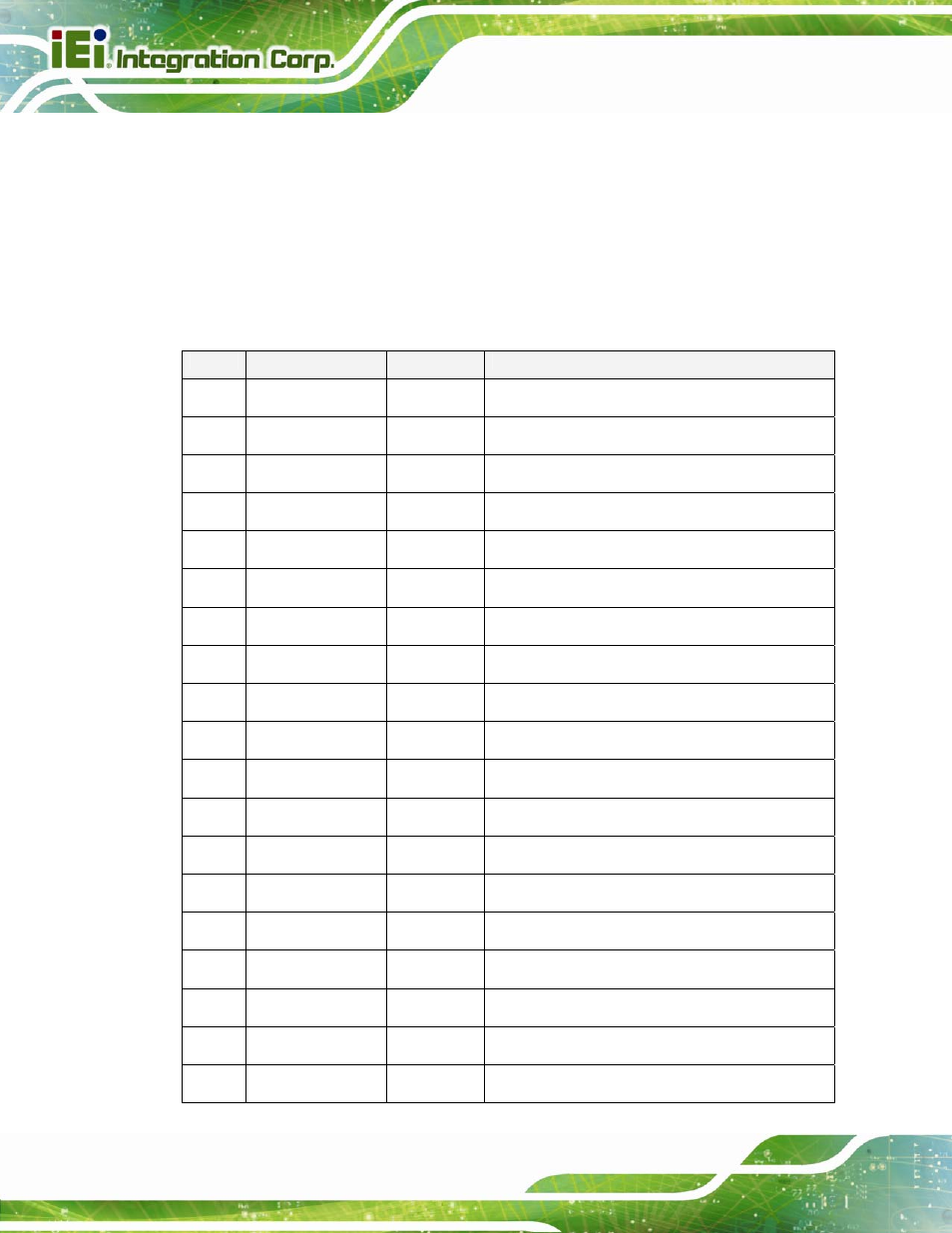

Pin

Signal

I/O

Description

C52

C53

PEG_RX0+

PEG_RX0-

I

PEG Port 0. Receive Input differential pair.

D52

D53

PEG_TX0+

PEG_TX0-

O

PEG Port 0. Transmit Output differential pair.

C55

C56

PEG_RX1+

PEG_RX1-

I

PEG Port 1. Receive Input differential pair.

D55

D56

PEG_TX1+

PEG_TX1-

O

PEG Port 1. Transmit Output differential pair.

C58

C59

PEG_RX2+

PEG_RX2-

I

PEG Port 2. Receive Input differential pair.

D58

D59

PEG_TX2+

PEG_TX2-

O

PEG Port 2. Transmit Output differential pair.

C61

C62

PEG_RX3+

PEG_RX3-

I

PEG Port 3. Receive Input differential pair.

D61

D62

PEG_TX3+

PEG_TX3-

O

PEG Port 3. Transmit Output differential pair.

C65

C66

PEG_RX4+

PEG_RX4-

I

PEG Port 4. Receive Input differential pair.

D65

D66

PEG_TX4+

PEG_TX4-

O

PEG Port 4. Transmit Output differential pair.

C68

C69

PEG_RX5+

PEG_RX5-

I

PEG Port 5. Receive Input differential pair.

D68

D69

PEG_TX5+

PEG_TX5-

O

PEG Port 5. Transmit Output differential pair.

C71

C72

PEG_RX6+

PEG_RX6-

I

PEG Port 6. Receive Input differential pair.

D71

D72

PEG_TX6+

PEG_TX6-

O

PEG Port 6. Transmit Output differential pair.

C74

C75

PEG_RX7+

PEG_RX7-

I

PEG Port 7. Receive Input differential pair.

D74

D75

PEG_TX7+

PEG_TX7-

O

PEG Port 7. Transmit Output differential pair.

C78

C79

PEG_RX8+

PEG_RX8-

I

PEG Port 8,. Receive Input differential pair.

D78

D79

PEG_TX8+

PEG_TX8-

O

PEG Port 8. Transmit Output differential pair.

C81

C82

PEG_RX9+

PEG_RX9-

I

PEG Port 9,. Receive Input differential pair.