Registers, Ee figure 94 – Rainbow Electronics AT89C5132 User Manual

Page 98

98

AT8xC5132

4173A–8051–08/02

Registers

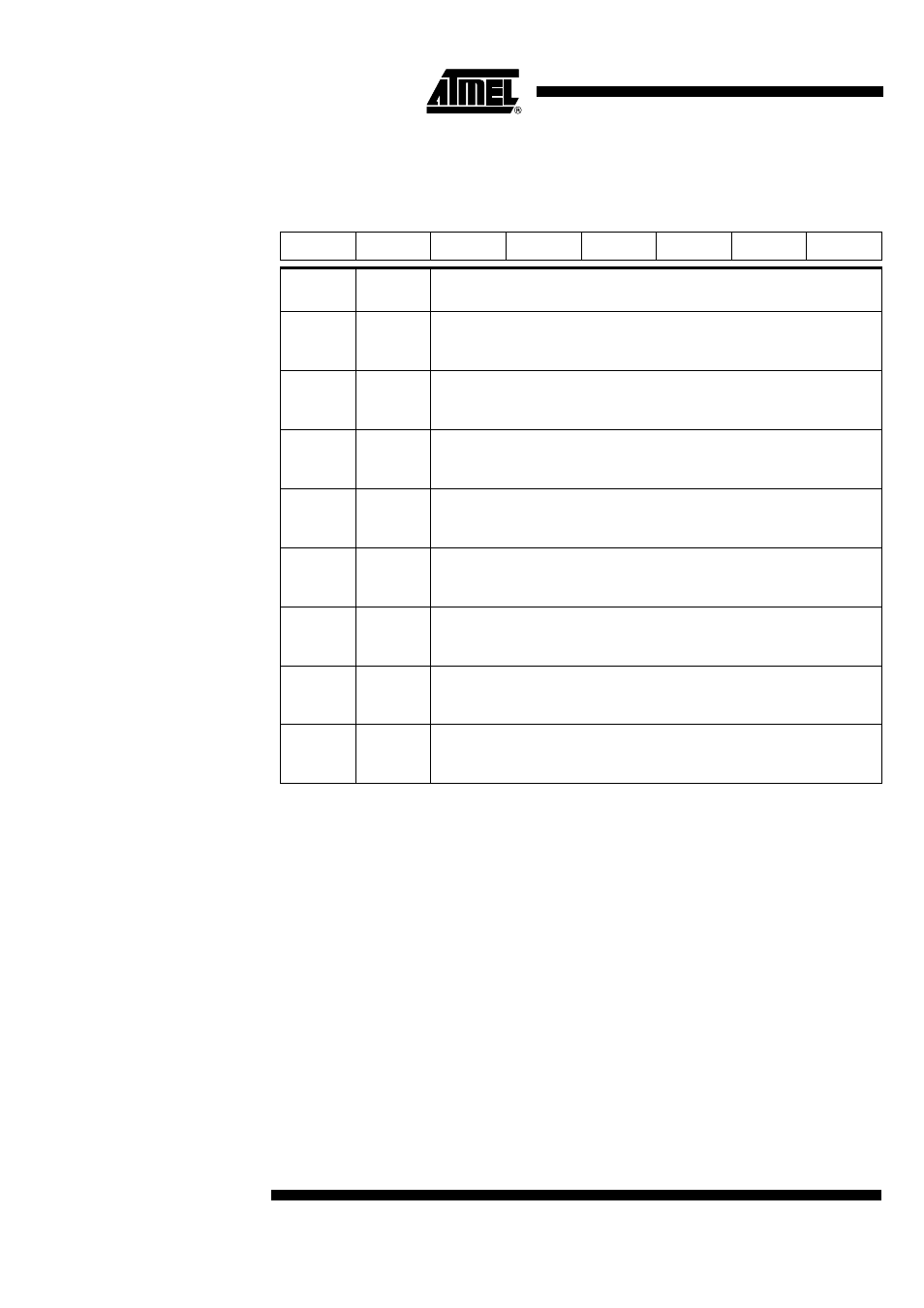

Table 94. MMCON0 Register

MMCON0 (S:E4h) – MMC Control Register 0

Reset Value = 0000 0000b

7

6

5

4

3

2

1

0

DRPTR

DTPTR

CRPTR

CTPTR

MBLOCK

DFMT

RFMT

CRCDIS

Bit

Number

Bit

Mnemonic

Description

7

DRPTR

Data Receive Pointer Reset Bit

Set to reset the read pointer of the data FIFO.

Clear to release the read pointer of the data FIFO.

6

DTPTR

Data Transmit Pointer Reset Bit

Set to reset the write pointer of the data FIFO.

Clear to release the write pointer of the data FIFO.

5

CRPTR

Command Receive Pointer Reset Bit

Set to reset the read pointer of the receive command FIFO.

Clear to release the read pointer of the receive command FIFO.

4

CTPTR

Command Transmit Pointer Reset Bit

Set to reset the write pointer of the transmit command FIFO.

Clear to release the read pointer of the transmit command FIFO.

3

MBLOCK

Multi-block Enable Bit

Set to select multi-block data format.

Clear to select single block data format.

2

DFMT

Data Format Bit

Set to select the block-oriented data format.

Clear to select the stream data format.

1

RFMT

Response Format Bit

Set to select the 48-bit response format.

Clear to select the 136-bit response format.

0

CRCDIS

CRC7 Disable Bit

Set to disable the CRC7 computation when receiving a response.

Clear to enable the CRC7 computation when receiving a response.