Rainbow Electronics AT89C5132 User Manual

Page 122

122

AT8xC5132

4173A–8051–08/02

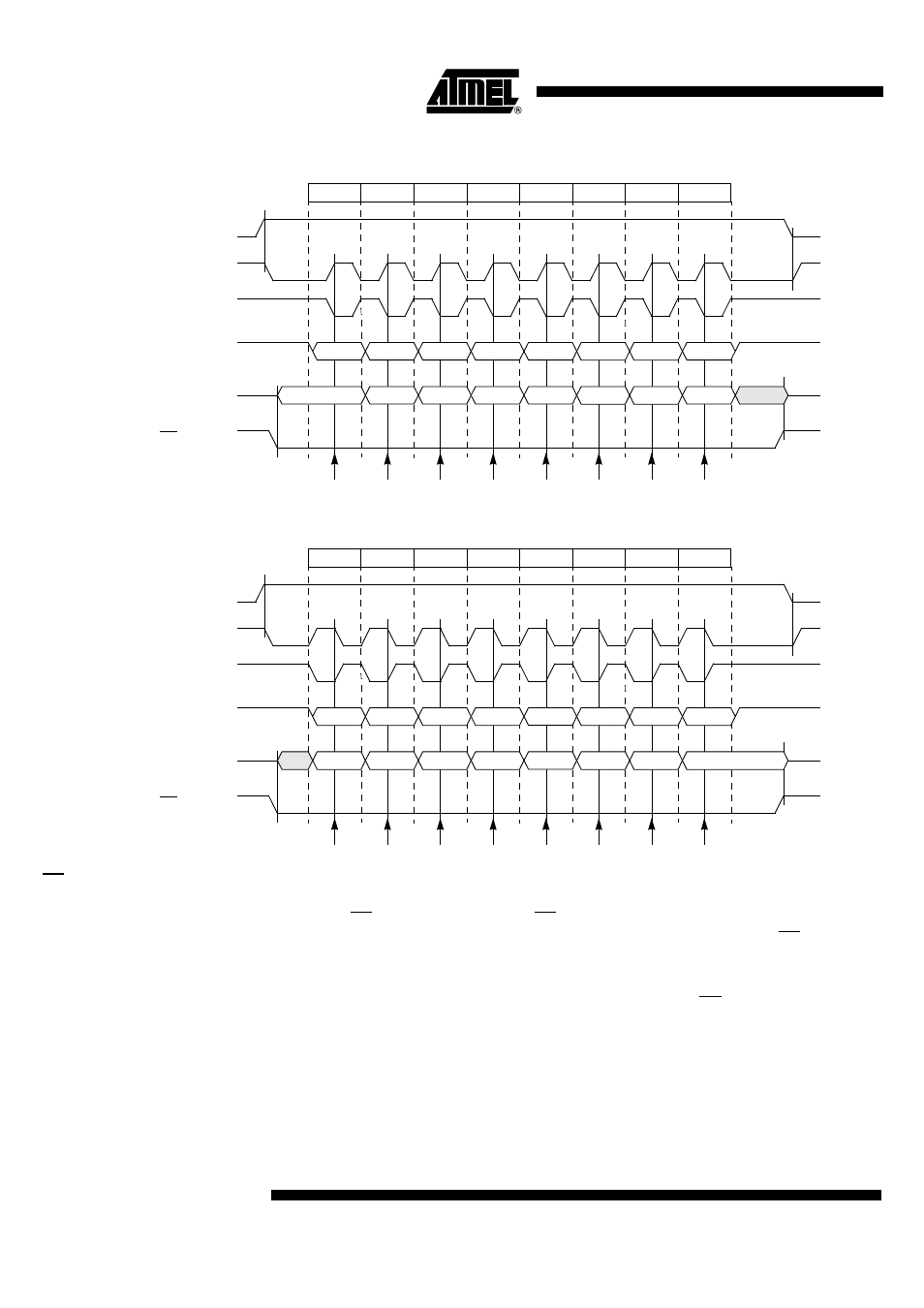

Figure 97. Data Transmission Format (CPHA = 0)

Figure 98. Data Transmission Format (CPHA = 1)

SS Management

Figure 97 shows an SPI transmission with CPHA = 0, where the first SCK edge is the

MSB capture point. Therefore the slave starts to output its MSB as soon as it is

selected: SS asserted to low level. SS must then be deasserted between each byte

transmission (see Figure 99). SPDAT must be loaded with data before SS is asserted

again.

Figure 98 shows an SPI transmission with CPHA = 1, where the first SCK edge is used

by the slave as a start of transmission signal. Therefore SS may remain asserted

between each byte transmission (see Figure 99).

1

2

3

4

5

6

7

8

MSB

bit 1

LSB

bit 2

bit 4

bit 3

bit 6

bit 5

bit 1

bit 2

bit 4

bit 3

bit 6

bit 5

MSB

LSB

MOSI (from Master)

MISO (from Slave)

SCK (CPOL = 1)

SCK (CPOL = 0)

SPEN (Internal)

SCK Cycle Number

SS (to Slave)

to Capture Point

1

2

3

4

5

6

7

8

MSB

bit 1

LSB

bit 2

bit 4

bit 3

bit 6

bit 5

bit 1

bit 2

bit 4

bit 3

bit 6

bit 5

MSB

LSB

MOSI (from Master)

MISO (from Slave)

SCK (CPOL = 1)

SCK (CPOL = 0)

SPEN (Internal)

SCK Cycle Number

SS (to Slave)

Capture Point