Rainbow Electronics AT89C5132 User Manual

Page 30

30

AT8xC5132

4173A–8051–08/02

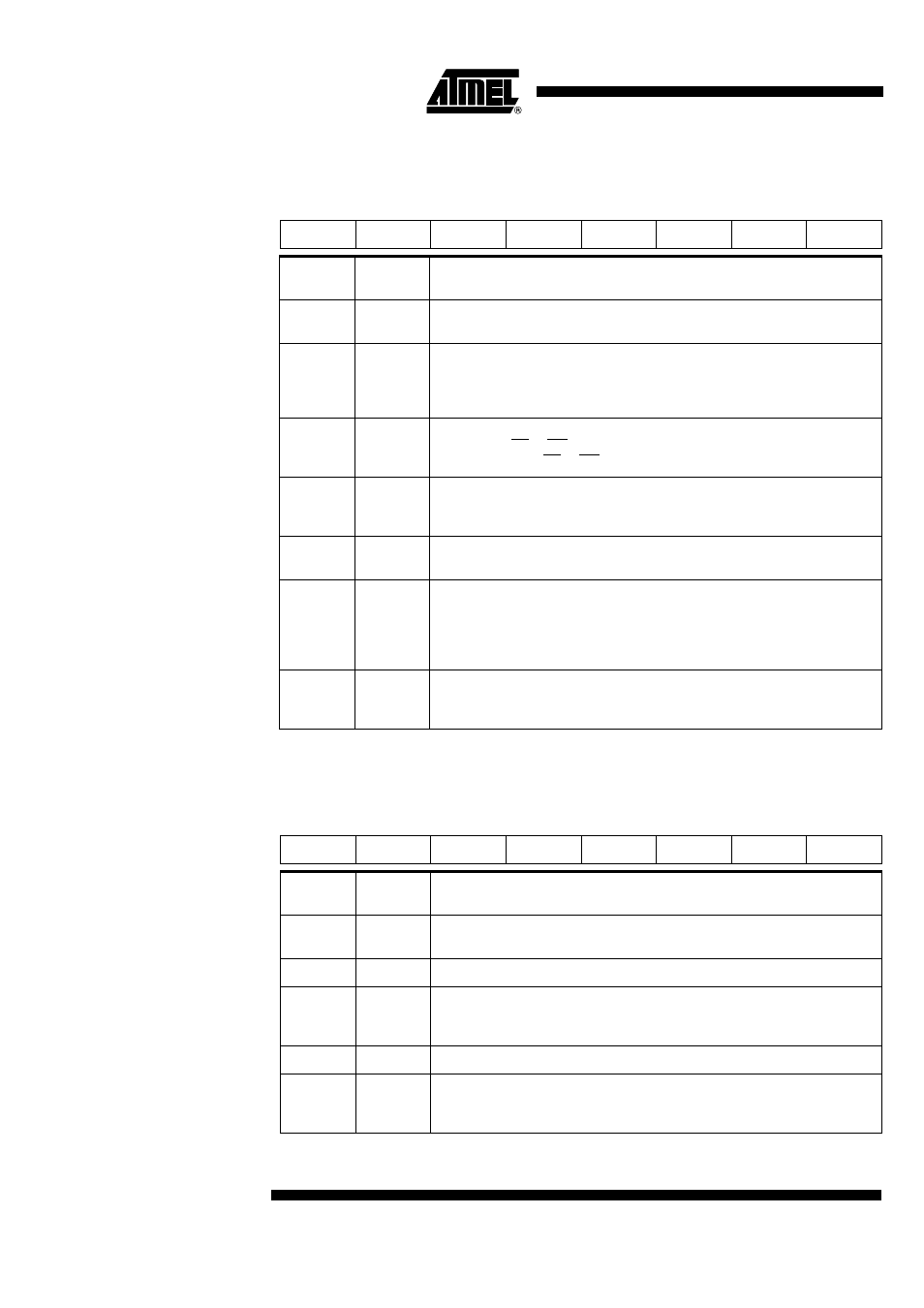

Table 28. AUXR Register

AUXR (S:8Eh) – Auxiliary Control Register

Reset Value = X000 1101b

Table 29. AUXR1 Register

AUXR1 (S:A2h) – Auxiliary Control Register 1

Reset Value = XXXX 00X0b

7

6

5

4

3

2

1

0

-

EXT16

M0

DPHDIS

XRS1

XRS0

EXTRAM

AO

Bit

Number

Bit

Mnemonic

Description

7

-

Reserved

The values read from this bit is indeterminate. Do not set this bit.

6

EXT16

External 16-bit Access Enable Bit

Set to enable 16-bit access mode during MOVX instructions.

Clear to disable 16-bit access mode and enable standard 8-bit access mode

during MOVX instructions.

5

M0

External Memory Access Stretch Bit

Set to stretch RD or WR signals duration to 15 CPU clock periods.

Clear not to stretch RD or WR signals and set duration to 3 CPU clock periods.

4

DPHDIS

DPH Disable Bit

Set to disable DPH output on P2 when executing MOVX @DPTR instruction.

Clear to enable DPH output on P2 when executing MOVX @DPTR instruction.

3 - 2

XRS1:0

Expanded RAM Size Bits

Refer to Table 25 for ERAM size description.

1

EXTRAM

External RAM Enable Bit

Set to select the external XRAM when executing MOVX @Ri or MOVX @DPTR

instructions.

Clear to select the internal expanded RAM when executing MOVX @Ri or MOVX

@DPTR instructions.

0

AO

ALE Output Enable Bit

Set to output the ALE signal only during MOVX instructions.

Clear to output the ALE signal at a constant rate of F

CPU

/3.

7

6

5

4

3

2

1

0

-

-

-

-

GF3

0

-

DPS

Bit

Number

Bit

Mnemonic

Description

7 - 4

-

Reserved

The values read from these Bits are indeterminate. Do not set these Bits.

3

GF3

General Purpose Flag 3.

2

0

Always Zero

This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3

flag.

1

-

Reserved for Data Pointer Extension.

0

DPS

Data Pointer Select Bit

Set to select second data pointer: DPTR1.

Clear to select first data pointer: DPTR0.