Rainbow Electronics AT89C5132 User Manual

Page 131

131

AT8xC5132

4173A–8051–08/02

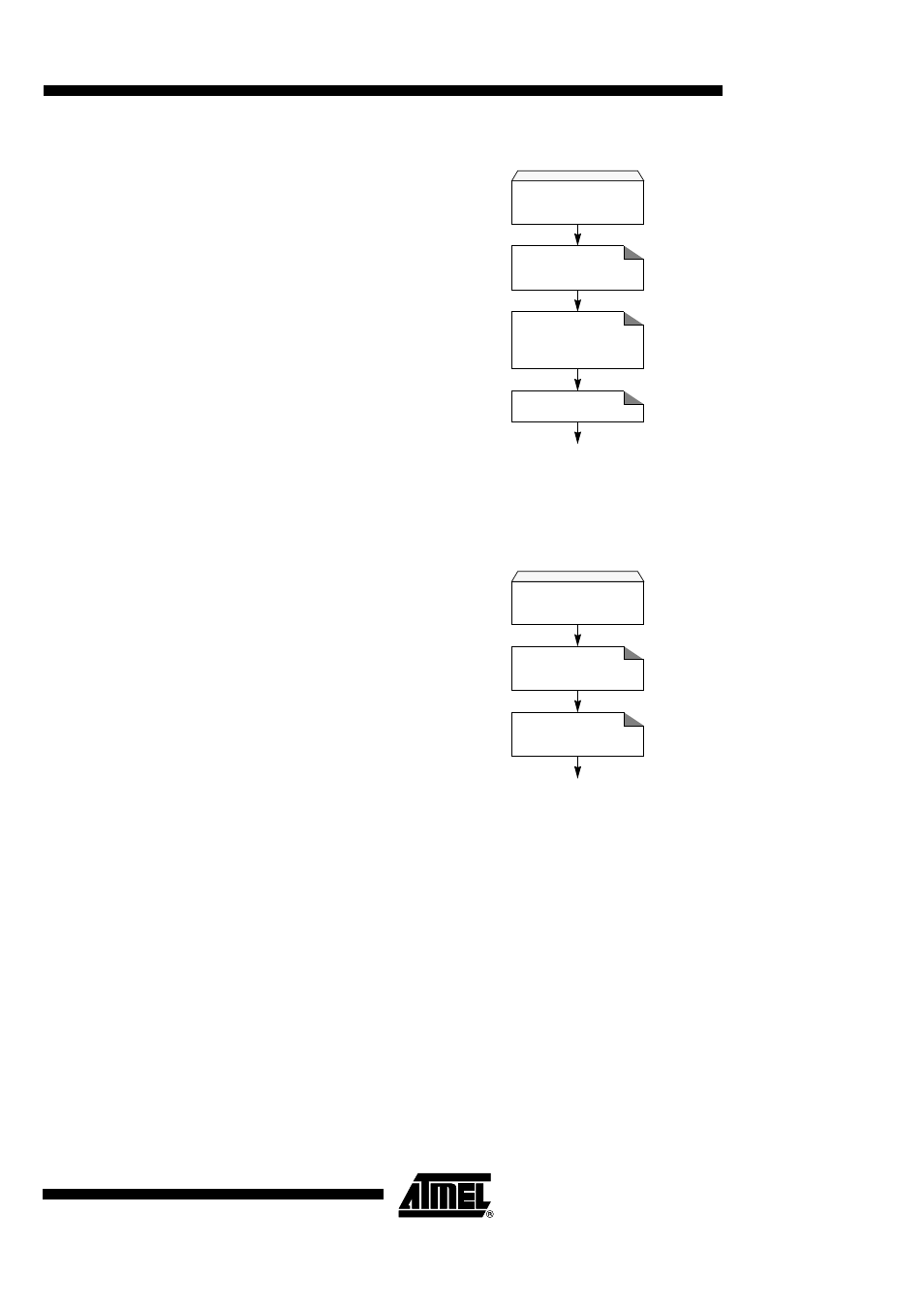

Figure 108. ADC Configuration Flow

Conversion Launching

The conversion is launched by setting the ADSST bit in ADCON register, this bit

remains set during the conversion. As soon as the conversion is started, it takes 11

clock periods (T

CONV

)

before the data is available in ADDH and ADDL registers.

Figure 109. ADC Conversion Launching Flow

End of Conversion

The end of conversion is signalled by the ADEOC flag in ADCON register becoming set

or by the ADSST bit in ADCON register becoming cleared.

The ADEOC flag can generate an interrupt if enabled by setting EADC bit in IEN1 regis-

ter. This flag is set by hardware and must be reset by software.

ADC

Configuration

Enable ADC

ADIDL = x

ADEN = 1

Wait Setup Time

Program ADC Clock

ADCD4:0 = xxxxxb

ADC

Conversion Start

Select Channel

ADCS = 0-1

Start Conversion

ADSST = 1

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)