Rainbow Electronics AT89C5132 User Manual

Page 78

78

AT8xC5132

4173A–8051–08/02

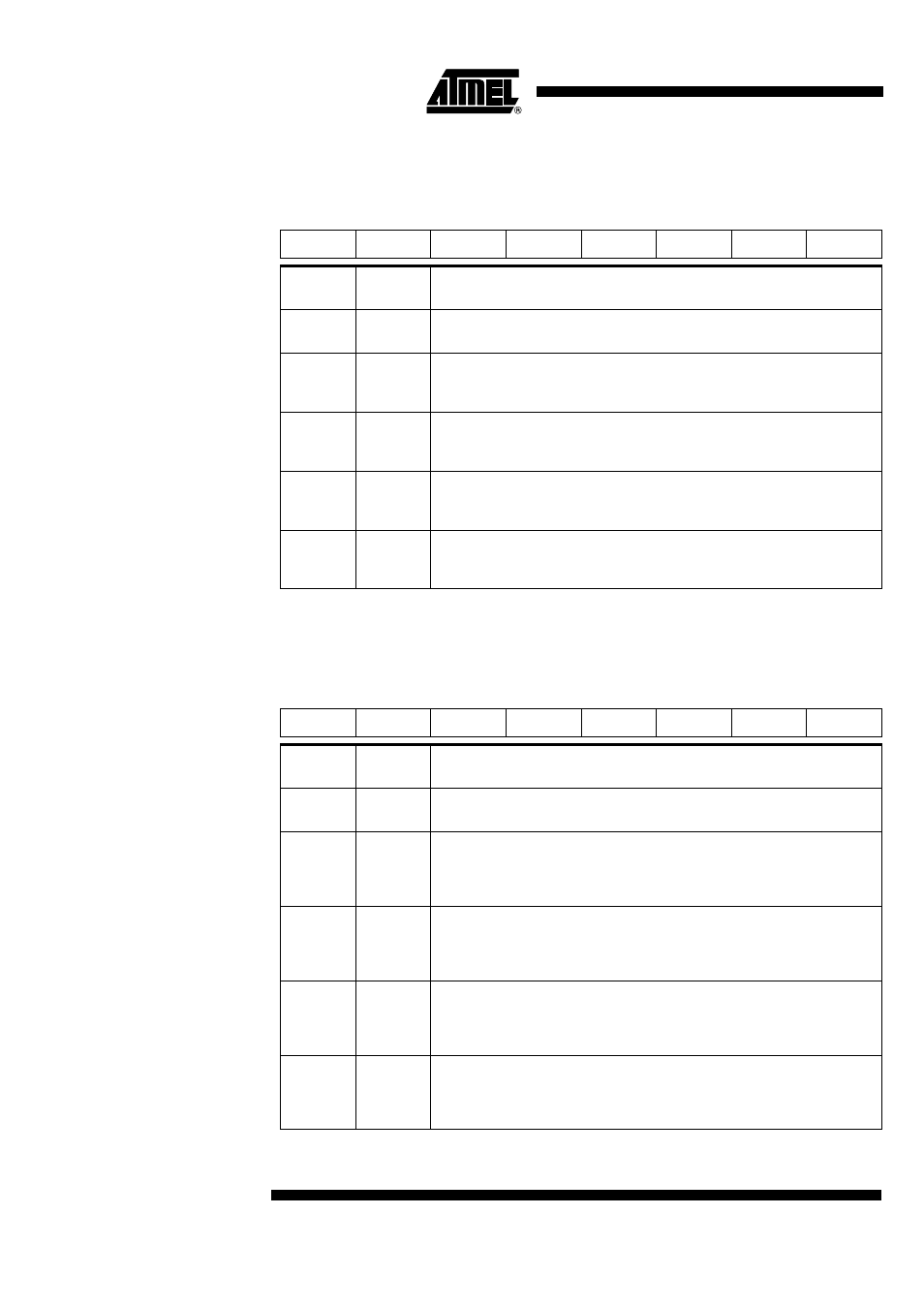

Table 79. UEPRST Register

UEPRST (S:D5h) – USB Endpoint FIFO Reset Register

Reset Value = 0000 0000b

Table 80. UEPINT Register

UEPINT (S:F8h Read-only) – USB Endpoint Interrupt Register

Reset Value = 0000 0000b

7

6

5

4

3

2

1

0

-

-

-

-

EP3RST

EP2RST

EP1RST

EP0RST

Bit

Number

Bit

Mnemonic

Description

7 - 4

-

Reserved

The values read from these Bits are always 0. Do not set these Bits.

3

EP3RST

Endpoint 3 FIFO Reset

Set and clear to reset the endpoint 3 FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

2

EP2RST

Endpoint 2 FIFO Reset

Set and clear to reset the endpoint 2 FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

1

EP1RST

Endpoint 1 FIFO Reset

Set and clear to reset the endpoint 1 FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

0

EP0RST

Endpoint 0 FIFO Reset

Set and clear to reset the endpoint 0 FIFO prior to any other operation, upon

hardware reset or when an USB bus reset has been received.

7

6

5

4

3

2

1

0

-

-

-

-

EP3INT

EP2INT

EP1INT

EP0INT

Bit

Number

Bit

Mnemonic

Description

7 - 4

-

Reserved

The values read from these Bits are always 0. Do not set these Bits.

3

EP3INT

Endpoint 3 Interrupt Flag

Set by hardware when an interrupt is triggered in UEPSTAX and the endpoint 3

interrupt is enabled in UEPIEN.

Must be cleared by software.

2

EP2INT

Endpoint 2 Interrupt Flag

Set by hardware when an interrupt is triggered in UEPSTAX and the endpoint 2

interrupt is enabled in UEPIEN.

Must be cleared by software.

1

EP1INT

Endpoint 1 Interrupt Flag

Set by hardware when an interrupt is triggered in UEPSTAX and the endpoint 1

interrupt is enabled in UEPIEN.

Must be cleared by software.

0

EP0INT

Endpoint 0 Interrupt Flag

Set by hardware when an interrupt is triggered in UEPSTAX and the endpoint 0

interrupt is enabled in UEPIEN.

Must be cleared by software.