Ee figure 99), Figure 100) – Rainbow Electronics AT89C5132 User Manual

Page 102

102

AT8xC5132

4173A–8051–08/02

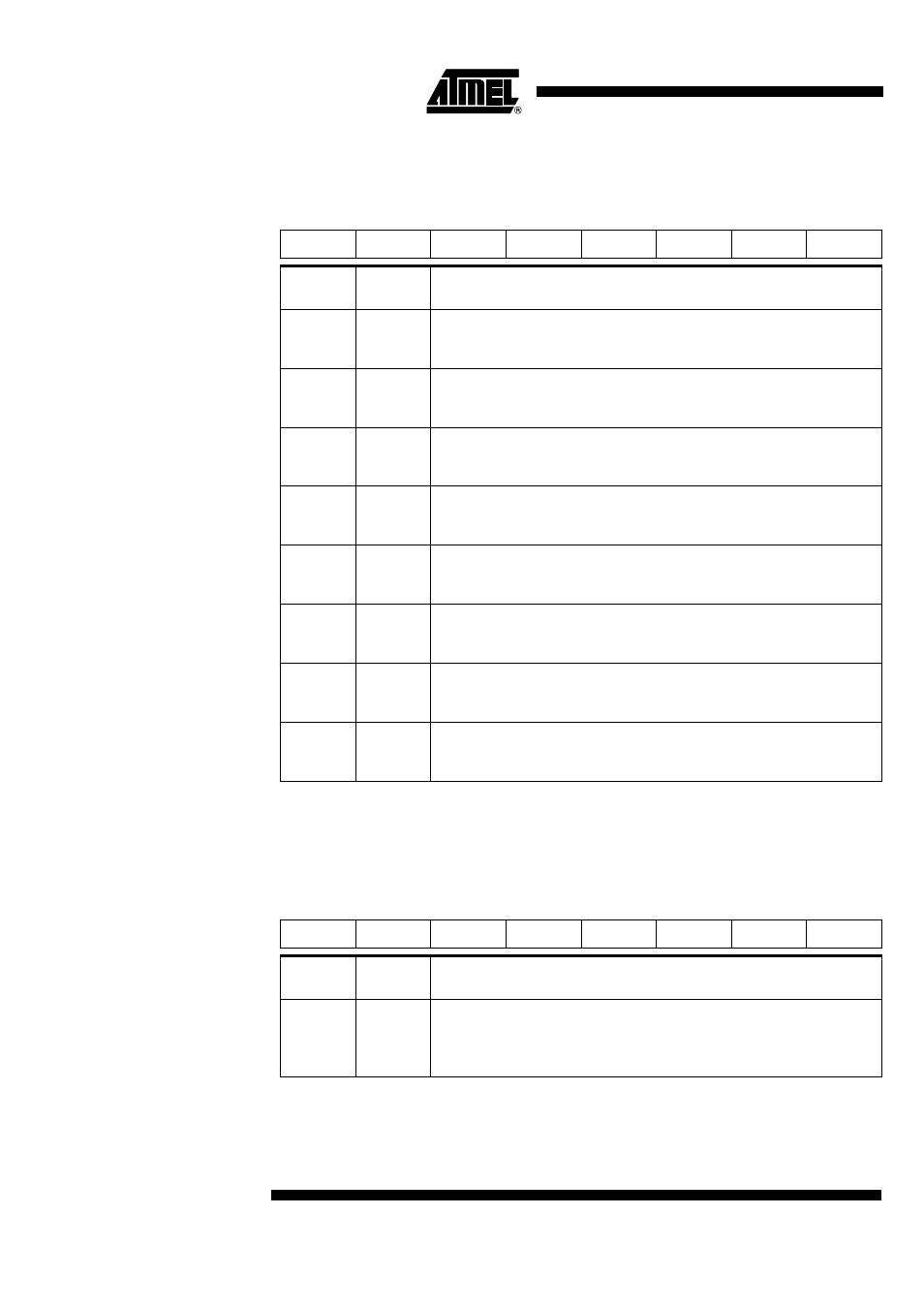

Table 99. MMMSK Register

MMMSK (S:DFh) – MMC Interrupt Mask Register

Reset Value = 1111 1111b

Table 100. MMCMD Register

MMCMD (S:DDh) – MMC Command Register

Reset Value = 1111 1111b

7

6

5

4

3

2

1

0

MCBM

EORM

EOCM

EOFM

F2FM

F1FM

F2EM

F1EM

Bit

Number

Bit

Mnemonic

Description

7

MCBM

MMC Card Busy Interrupt Mask Bit

Set to prevent MCBI flag from generating an MMC interrupt.

Clear to allow MCBI flag to generate an MMC interrupt.

6

EORM

End Of Response Interrupt Mask Bit

Set to prevent EORI flag from generating an MMC interrupt.

Clear to allow EORI flag to generate an MMC interrupt.

5

EOCM

End Of Command Interrupt Mask Bit

Set to prevent EOCI flag from generating an MMC interrupt.

Clear to allow EOCI flag to generate an MMC interrupt.

4

EOFM

End Of Frame Interrupt Mask Bit

Set to prevent EOFI flag from generating an MMC interrupt.

Clear to allow EOFI flag to generate an MMC interrupt.

3

F2FM

FIFO 2 Full Interrupt Mask Bit

Set to prevent F2FI flag from generating an MMC interrupt.

Clear to allow F2FI flag to generate an MMC interrupt.

2

F1FM

FIFO 1 Full Interrupt Mask Bit

Set to prevent F1FI flag from generating an MMC interrupt.

Clear to allow F1FI flag to generate an MMC interrupt.

1

F2EM

FIFO 2 Empty Interrupt Mask Bit

Set to prevent F2EI flag from generating an MMC interrupt.

Clear to allow F2EI flag to generate an MMC interrupt.

0

F1EM

FIFO 1 Empty Interrupt Mask Bit

Set to prevent F1EI flag from generating an MMC interrupt.

Clear to allow F1EI flag to generate an MMC interrupt.

7

6

5

4

3

2

1

0

MC7

MC6

MC5

MC4

MC3

MC2

MC1

MC0

Bit

Number

Bit

Mnemonic

Description

7 - 0

MC7:0

MMC Command Receive Byte

Output (read) register of the response FIFO.

MMC Command Transmit Byte

Input (write) register of the command FIFO.