Description – Rainbow Electronics AT89C5132 User Manual

Page 69

69

AT8xC5132

4173A–8051–08/02

Description

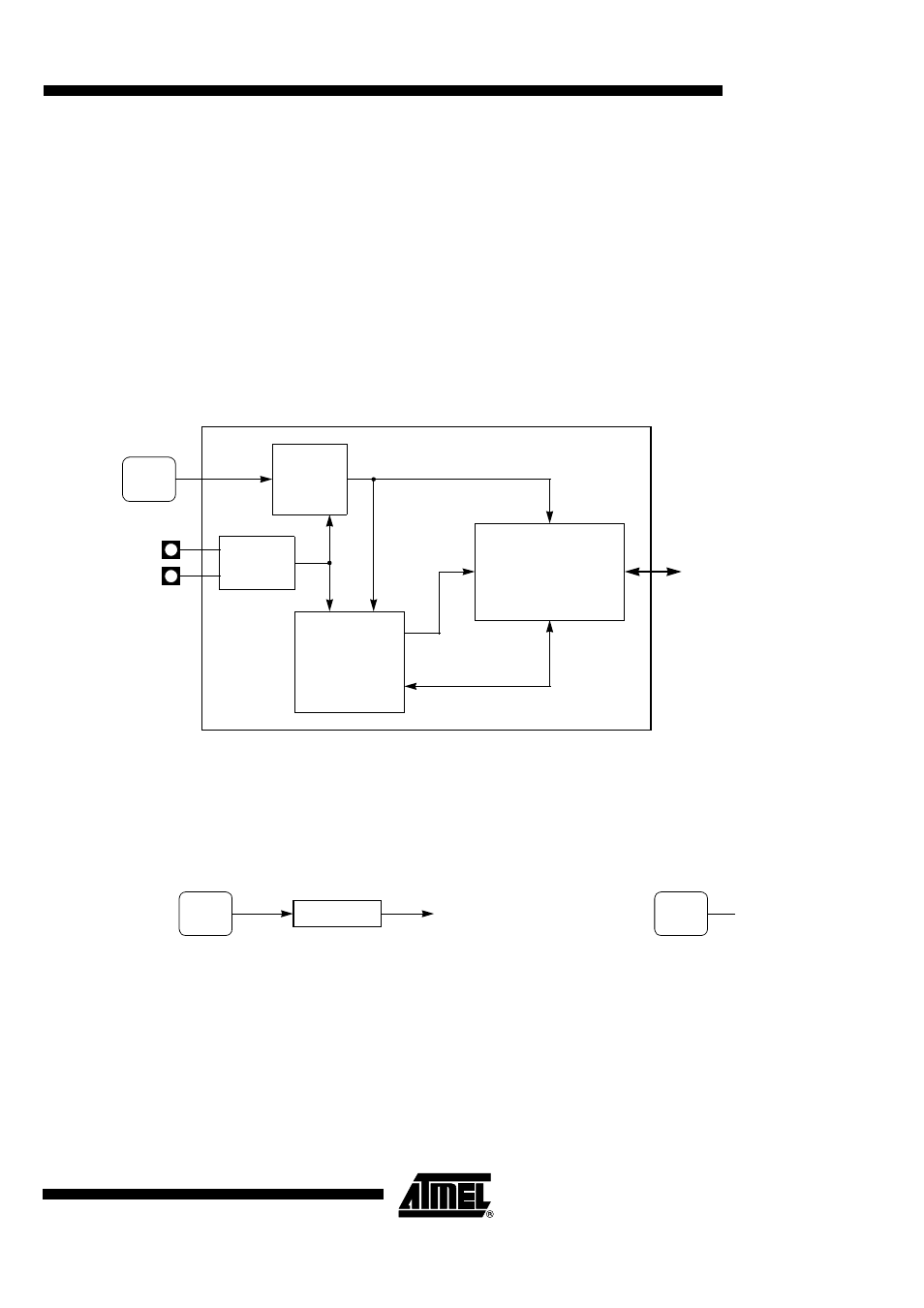

The USB device controller provides the hardware that the AT8xC5132 need to interface

a USB link to data flow stored in a double port memory.

It requires a 48 MHz reference clock provided by the clock controller as detailed in Sec-

tion "Clock Controller", page 69. This clock is used to generate a 12 MHz full speed bit

clock from the received USB differential data flow and to transmit data according to full

speed USB device tolerance. Clock recovery is done by a Digital Phase Locked Loop

(DPLL) block.

The Serial Interface Engine (SIE) block performs NRZI encoding and decoding, bit stuff-

ing, CRC generation and checking, and the serial-parallel data conversion.

The Universal Function Interface (UFI) controls the interface between the data flow and

the Dual Port RAM, but also the interface with the C51 core itself.

Figure 46. USB Device Controller Block Diagram

Clock Controller

The USB controller clock is generated by division of the PLL clock. The division factor is

given by USBCD1:0 Bits in USBCLK register (see Table 86). Figure 47 shows the USB

controller clock generator and its calculation formula. The USB controller clock fre-

quency must always be 48 MHz.

Figure 47. USB Clock Generator and Symbol

USB

CLOCK

48 MHz

12 MHz

D+

D-

DPLL

SIE

UFI

USB

Buffer

To/From C51 Core

USBCD1:0

USBCLK

48 MHz USB Clock

USBclk

PLLclk

USBCD

1

+

--------------------------------

=

USB

CLOCK

USB Clock Symbol

PLL

CLOCK