Clock generator, Data converter – Rainbow Electronics AT89C5132 User Manual

Page 62

62

AT8xC5132

4173A–8051–08/02

Clock Generator

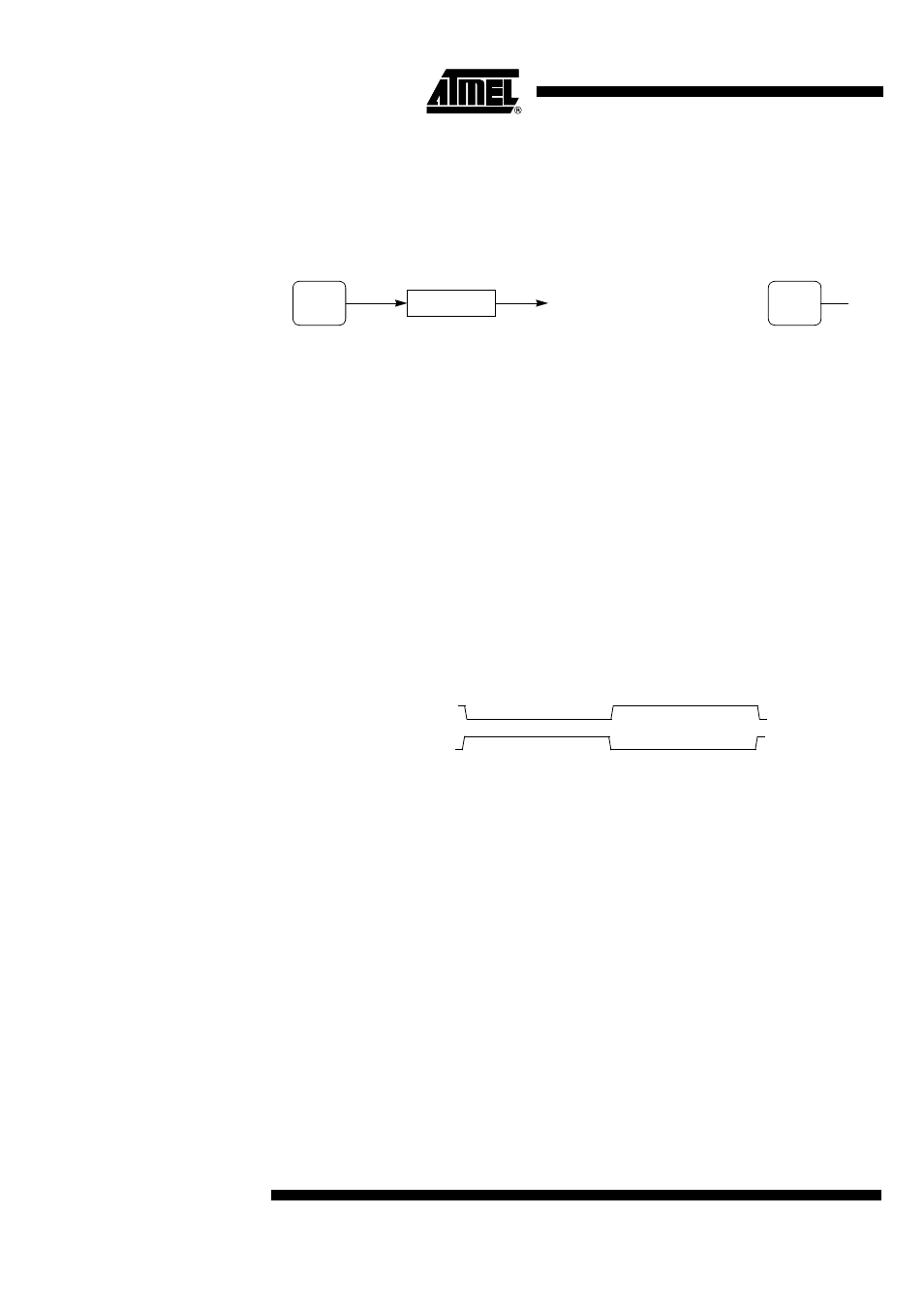

The audio interface clock is generated by division of the PLL clock. The division factor is

given by AUCD4:0 Bits in AUDCLK register. Figure 41 shows the audio interface clock

generator and its calculation formula. The audio interface clock frequency depends on

the audio DAC used.

Figure 41. Audio Clock Generator and Symbol

As soon as audio interface is enabled by setting AUDEN bit in AUDCON1 register, the

master clock generated by the PLL is output on the SCLK pin which is the DAC system

clock. This clock is output at 256 or 384 times the sampling frequency depending on the

DAC capabilities. HLR bit in AUDCON0 register must be set according to this rate for

properly generating the audio bit clock on the DCLK pin and the word selection clock on

the DSEL pin. These clocks are not generated when no data is available at the data

converter input.

For DAC compatibility, the bit clock frequency is programmable for outputting 16 Bits or

32 Bits per channel using the DSIZ bit in AUDCON0 register (see Section "Data Con-

verter", page 62), and the word selection signal is programmable for outputting left

channel on low or high level according to POL bit in AUDCON0 register as shown in

Figure 42.

Figure 42. DSEL Output Polarity

Data Converter

The data converter block converts the audio stream input from the 16-bit parallel format

to a serial format. For accepting all PCM formats and I

2

S format, JUST4:0 Bits in

AUDCON0 register are used to shift the data output point. As shown in Figure 43, these

Bits allow MSB justification by setting JUST4:0 = 00000, LSB justification by setting

JUST4:0 = 10000, I

2

S Justification by setting JUST4:0 = 00001, and more than 16-bit

LSB justification by filling the low significant Bits with logic 0.

AUCD4:0

AUDCLK

Audio Interface Clock

AUDclk

PLLclk

AUCD

1

+

---------------------------

=

Audio Clock Symbol

AUD

CLOCK

PLL

CLOCK

Left Channel

Right Channel

POL = 1

POL = 0

Left Channel

Right Channel