Rainbow Electronics AT89C5132 User Manual

Page 111

111

AT8xC5132

4173A–8051–08/02

Framing Error Detection

(Modes 1, 2 and 3)

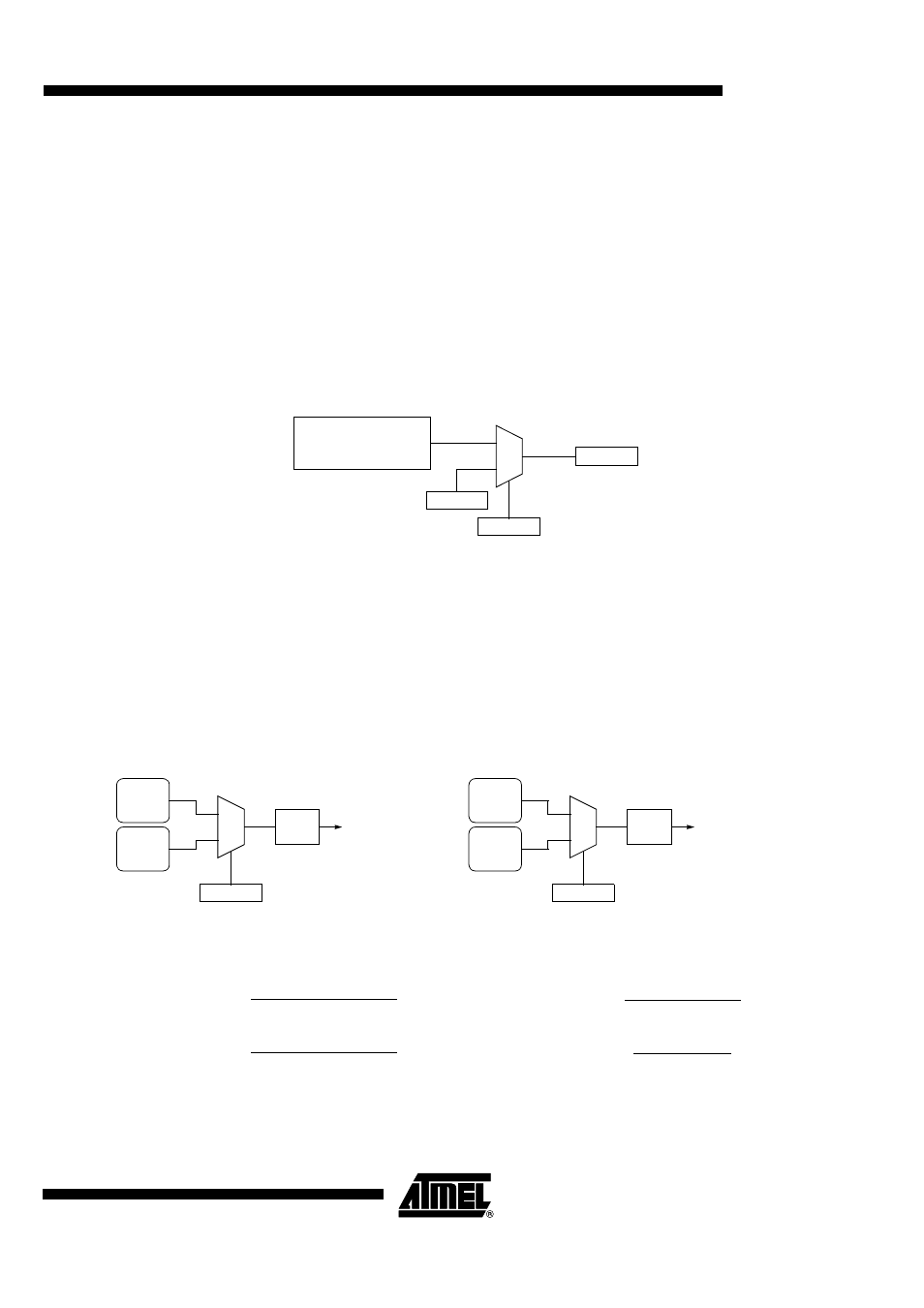

Framing error detection is provided for the three asynchronous modes. To enable the

framing bit error detection feature, set SMOD0 bit in PCON register as shown in

Figure 86.

When this feature is enabled, the receiver checks each incoming data frame for a valid

stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous

transmission by two devices. If a valid stop bit is not found, the software sets FE bit in

SCON register.

Software may examine FE bit after each reception to check for data errors. Once set,

only software or a chip reset clears FE bit. Subsequently received frames with valid stop

Bits cannot clear FE bit. When the framing error detection feature is enabled, RI rises on

stop bit instead of the last data bit as detailed in Figure 92.

Figure 86. Framing Error Block Diagram

Baud Rate Selection (Modes 1

and 3)

In modes 1 and 3, the Baud Rate is derived either from the Timer 1 or the Internal Baud

Rate Generator and allows different baud rate in reception and transmission.

As shown in Figure 87, the selection is done using RBCK and TBCK Bits in BDRCON

register.

Figure 88 gives the baud rate calculation formulas for each baud rate source. Table 106

details Internal Baud Rate Generator configuration for different peripheral clock frequen-

cies and gives baud rates closer to the standard baud rates.

Figure 87. Baud Rate Source Selection (Modes 1 and 3)

Figure 88. Baud Rate Formulas (Modes 1 and 3)

SM0

1

0

SMOD0

PCON.6

SM0/FE

SCON.7

Framing Error

Controller

FE

0

1

RBCK

BDRCON.2

T1

CLOCK

To Serial

IBRG

CLOCK

Reception Port

0

1

TBCK

BDRCON.3

T1

CLOCK

To Serial

IBRG

CLOCK

Transmission Port

ч

16

ч

16

Baud_Rate=

6

(1-SPD)

⋅

32

⋅

(256 -BRL)

2

SMOD1

⋅

F

PER

BRL= 256 -

6

(1-SPD)

⋅

32

⋅

Baud_Rate

2

SMOD1

⋅

F

PER

Baud_Rate=

6 Ю 32 Ю (256 -TH1)

2

SMOD1

⋅

F

PER

TH1= 256 -

192

⋅

Baud_Rate

2

SMOD1

⋅

F

PER

A. IBRG Formula

B. T1 Formula