Registers, Table 67 and table 68) – Rainbow Electronics AT89C5132 User Manual

Page 66

66

AT8xC5132

4173A–8051–08/02

Registers

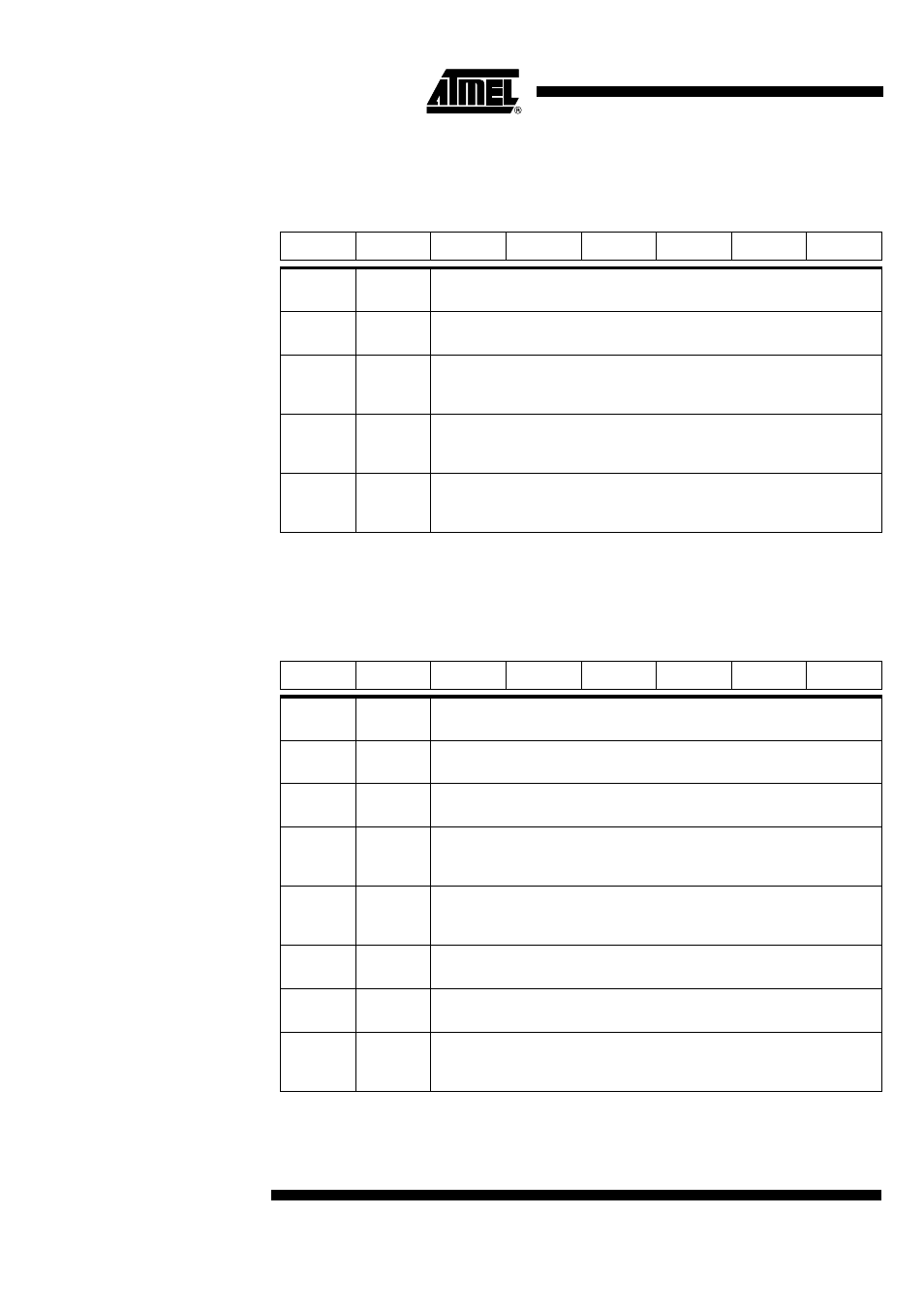

Table 67. AUDCON0 Register

AUDCON0 (S:9Ah) – Audio Interface Control Register 0

Reset Value = 0000 1000b

Table 68. AUDCON1 Register

AUDCON1 (S:9Bh) – Audio Interface Control Register 1

Reset Value = 1011 0010b

7

6

5

4

3

2

1

0

JUST4

JUST3

JUST2

JUST1

JUST0

POL

DSIZ

HLR

Bit

Number

Bit

Mnemonic

Description

7 - 3

JUST4:0

Audio Stream Justification Bits

Refer to Section "Data Converter", page 62 for Bits description.

2

POL

DSEL Signal Output Polarity

Set to output the left channel on high level of DSEL output (PCM mode).

Clear to output the left channel on the low level of DSEL output (I

2

S mode).

1

DSIZ

Audio Data Size

Set to select 32-bit data output format.

Clear to select 16-bit data output format.

0

HLR

High/Low Rate Bit

Set by software when the PLL clock frequency is 384·Fs.

Clear by software when the PLL clock frequency is 256·Fs.

7

6

5

4

3

2

1

0

–

–

MSREQ

MUDRN

-

DUP1

DUP0

AUDEN

Bit

Number

Bit

Mnemonic

Description

7

–

Reserved

The values read from this bit is always 0. Do not set this bit.

6

–

Reserved

The values read from this bit is always 0. Do not set this bit.

5

MSREQ

Audio Sample Request Flag Mask Bit

Set to prevent the SREQ flag from generating an audio interrupt.

Clear to allow the SREQ flag to generate an audio interrupt.

4

MUDRN

Audio Sample Under-run Flag Mask Bit

Set to prevent the UDRN flag from generating an audio interrupt.

Clear to allow the UDRN flag to generate an audio interrupt.

3

–

Reserved

The values read from this bit is always 0. Do not set this bit.

2 - 1

DUP1:0

Audio Duplication Factor

Refer to Table 66 for Bits description.

0

AUDEN

Audio Interface Enable Bit

Set to enable the audio interface.

Clear to disable the audio interface.